# **CHAPTER 3**

# **DIGITAL MOS CIRCUITS**

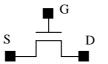

- 3.1 The MOS Transistor

- 3.2 The MOS Switches

- 3.3 Static CMOS Circuits

- 3.4 Dynamic MOS Circuits

- 3.5 MOS Circuit Performance

- 3.6 BiCMOS Digital Circuit

- 3.7 CMOS Fabrication Process

# 3.1 The MOS TRANSISTOR

MOS integrated circuits use MOSFET (Metal Oxide Semiconductor Field Effect Transistor), which are 4-terminal device, as the building block. Two basic types of MOSFET are the NMOS (n-channel device) and PMOS (p-channel device) transistors.

# **3.1.1 MOS Characteristics**

MOSFET is a voltage-controlled device. The gate-source voltage,  $V_{gs}$ , controls the channel width and hence the amount of current through the device.

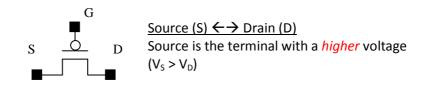

Although MOS transistors are symmetrical device, by convention the majority carriers (electrons for NMOS and holes for PMOS) flow from the source to the drain. Thus, for NMOS, the source terminal is usually of a lower potential than the drain while in PMOS, source is usually of higher potential than the drain.

The input impedance at the gate terminal is also very high thus the gate current is very small, that is,  $I_G \sim 0$ . As the gate terminal is isolated from the channel/substrate by a layer of oxide, it basically presents itself as a capacitive load to an input signal.

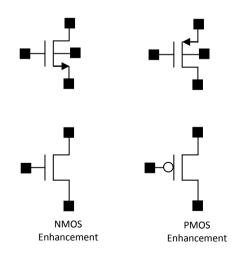

## **3.1.2 MOS Transistor Symbols**

Figure 3-1 shows various symbols used for the different types of MOS transistors. Those on the top row are symbols with 4 terminals. The terminal in the center is the Bulk (B) terminal. As the Bulk terminal is usually connected to the source terminal, simplified symbols as shown in the second row are the more commonly used in circuit representation.

Figure 3-1 MOS Transistor Symbols (4 Terminals & 3 Terminals)

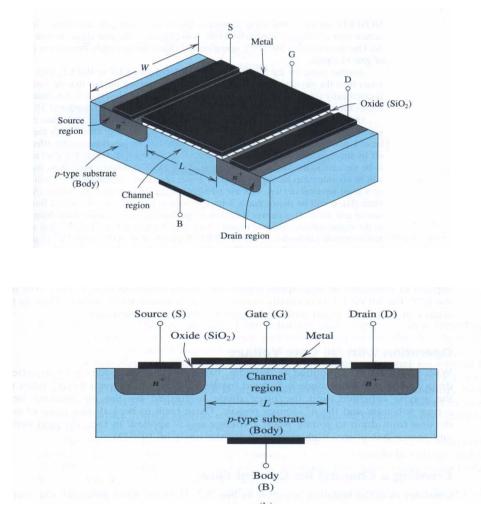

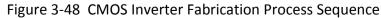

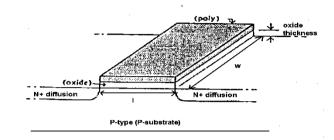

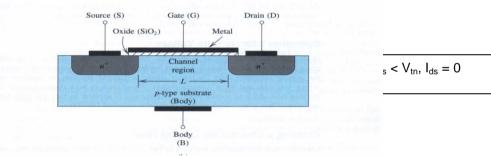

### 3.1.3 Basic NMOS Device Structure

Figure 3-2 shows the physical and cross sectional structure of a NMOS transistor. It is formed on a p-type substrate. The source and drain regions are formed by introducing impurities of type VI (P or As) into the p-type substrate until the region becomes a n-type semiconductor.

The distance between the source and drain is defined as the channel length and it is parallel to the direction of current flow. Channel width of the transistor is the dimension perpendicular to the direction of current flow. The channel length and width affect the performance of a MOS transistor.

Figure 3-2 Physical & Cross Sectional Structure of NMOS Transistor

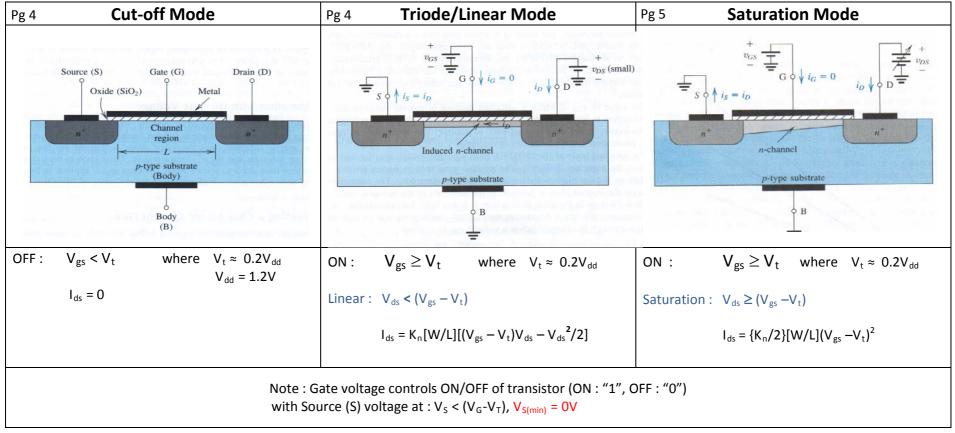

# **3.1.4 Operation of NMOS Enhancement Transistor**

A basic enhancement mode MOSFET does not have a channel established at fabrication thus it is a normally OFF device. The transistor have 3 modes of operation, namely :-

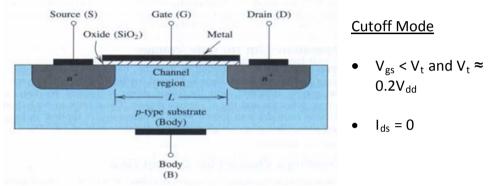

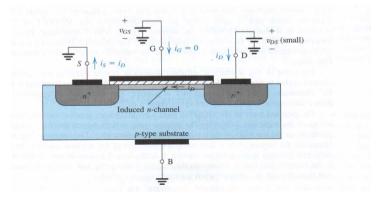

#### (i) <u>Cut-off Mode</u>

When the voltage applied to the gate of the transistor is such that  $V_{gs} < V_t$ , where  $V_t \approx 0.2V_{dd}$ , no conducting channel is induced resulting in the path resistance between the source and drain being very high and hence  $I_{ds} = 0$ .

Figure 3-3 NMOS transistor in Cutoff Mode Operation

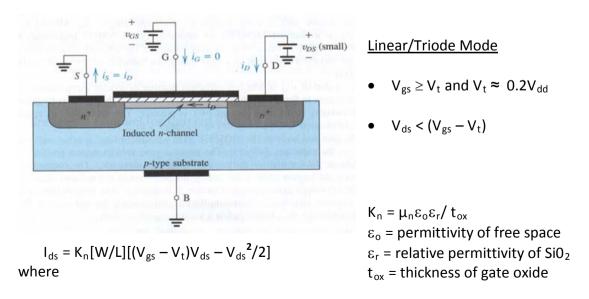

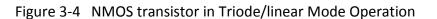

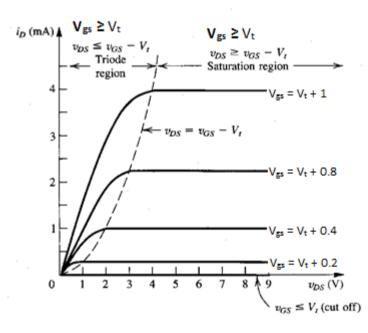

### (ii) Triode/Linear Mode

When  $V_{gs} \ge V_t$  and  $V_{ds} < (V_{gs} - V_t)$ , electrons (carriers) accumulated near the surface under the gate region starts to gather to create a conducting channel between the source and the drain. With the channel, current can now flow from the drain to the source (opposite to electron flow). In this region,  $I_{ds}$  increases with both the drain and gate voltage.

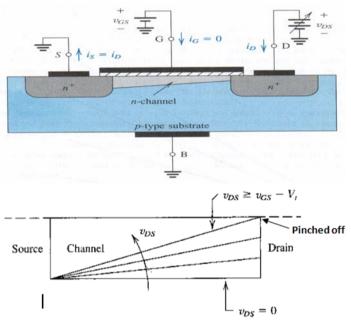

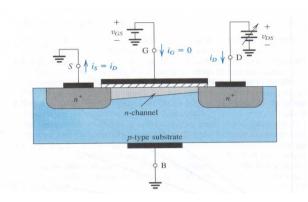

#### (iii) Saturation Mode

When  $V_{gs} \ge V_t$  and  $V_{ds} \ge (V_{gs} - V_t)$ , the channel will become tapered, as shown in Figure 3-5, because the effective voltage on the channel decreases towards the drain end. In this region, the current  $I_{ds}$  ceased to be influenced by the drain voltage. The  $I_{ds}$  under this condition is given as :-

#### Saturation Mode

- $V_{gs} \ge V_t$  and  $V_t \approx 0.2V_{dd}$

- $V_{ds} \ge (V_{gs} V_t)$

- $I_{ds} = \{K_n/2\}[W/L](V_{gs} V_t)^2$

where

$$\begin{split} & K_n = \mu_n \varepsilon_o \varepsilon_r / t_{ox} \\ & \varepsilon_o = \text{permittivity of free space} \\ & \varepsilon_r = \text{relative permittivity of SiO}_2 \\ & t_{ox} = \text{thickness of gate oxide} \end{split}$$

Figure 3-5 NMOS Transistor in Saturation Mode

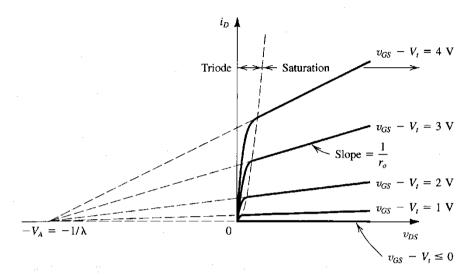

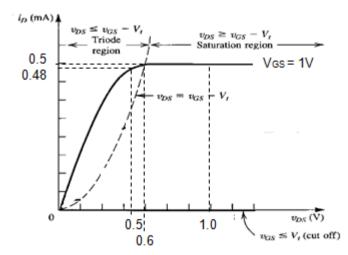

Figure 3-6 NMOS Ids vs Vds Characteristic Curve

In summary, the equations for NMOS enhancement transistor are :-

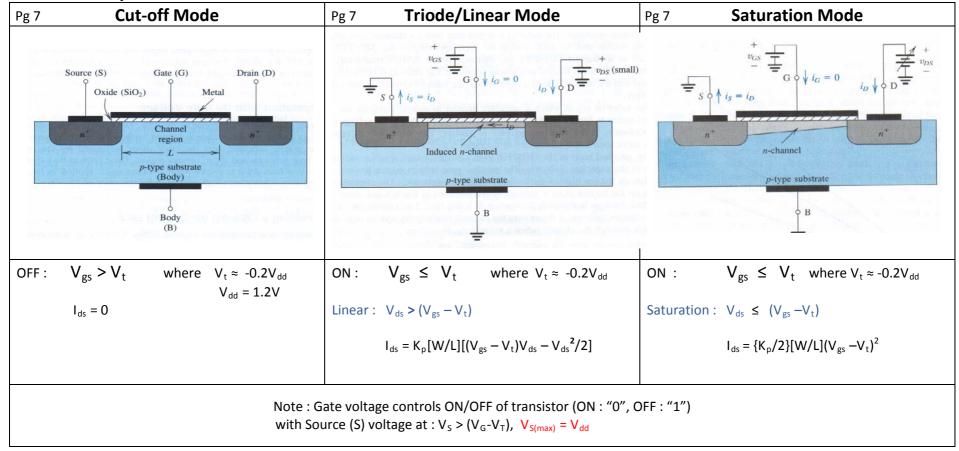

# 3.1.5 PMOS transistor

PMOS transistor needs a N-type substrate with both source and drain doped with type III impurities (Boron) to form p-type regions. The threshold voltage (V<sub>t</sub>) is approximately -0.2V<sub>dd</sub>. To turn ON an enhancement PMOS, a gate-source voltage of  $V_{gs} \leq V_t$  is required.

The equations for PMOS enhancement transistor are :-

OFF:  $V_{gs} > V_t$  where  $V_t \approx -0.2V_{dd}$

$\mathsf{ON}: \quad \mathsf{V}_{\mathsf{gs}} \leq \mathsf{V}_{\mathsf{t}}$

(b) Linear Region :  $V_{ds} > (V_{gs} - V_t)$  $I_{ds} = K_p[W/L][(V_{gs} - V_t)V_{ds} - V_{ds}^2/2]$

(b) Saturation Region :  $V_{ds} \leq (V_{gs} - V_t)$  $I_{ds} = [K_p/2][W/L](V_{gs} - V_t)^2$

|                       | NMOS                                                     | PMOS                                                   |

|-----------------------|----------------------------------------------------------|--------------------------------------------------------|

| OFF                   | $V_{gs} < V_t$ where $V_t \approx 0.2V_{dd}$             | $V_{gs} > V_t$ where $V_t \approx -0.2V_{dd}$          |

| ON :<br>Linear Region | $V_{gs} \ge V_t$                                         | V <sub>gs</sub> ≤ V <sub>t</sub>                       |

|                       | $V_{ds} < (V_{gs} - V_t)$                                | $V_{ds}$ > ( $V_{gs} - V_t$ )                          |

|                       | $I_{ds} = K_n [W/L] [(V_{gs} - V_t)V_{ds} - V_{ds}^2/2]$ | $I_{ds} = K_p[W/L][(V_{gs} - V_t)V_{ds} - V_{ds}^2/2]$ |

| ON :<br>Saturation    | $V_{ds} \geq (V_{gs} - V_t)$                             | $V_{ds} \leq (V_{gs} - V_t)$                           |

| Region                | $I_{ds} = [K_n/2][W/L](V_{gs} - V_t)^2$                  | $I_{ds} = [K_p/2][W/L](V_{gs} - V_t)^2$                |

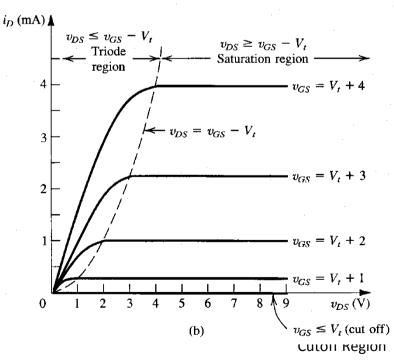

# **3.2 THE MOS SWITCHES**

Transistors can be biased to operate as switches. In the case of MOS transistor, a control signal (SN) can be applied to the gate of the device to turn it ON or OFF.

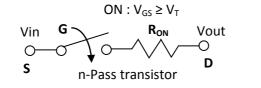

Figure 3-7 A Simple Switch Representation

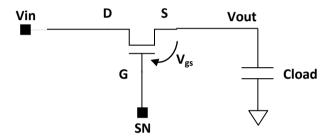

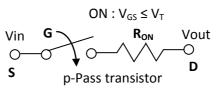

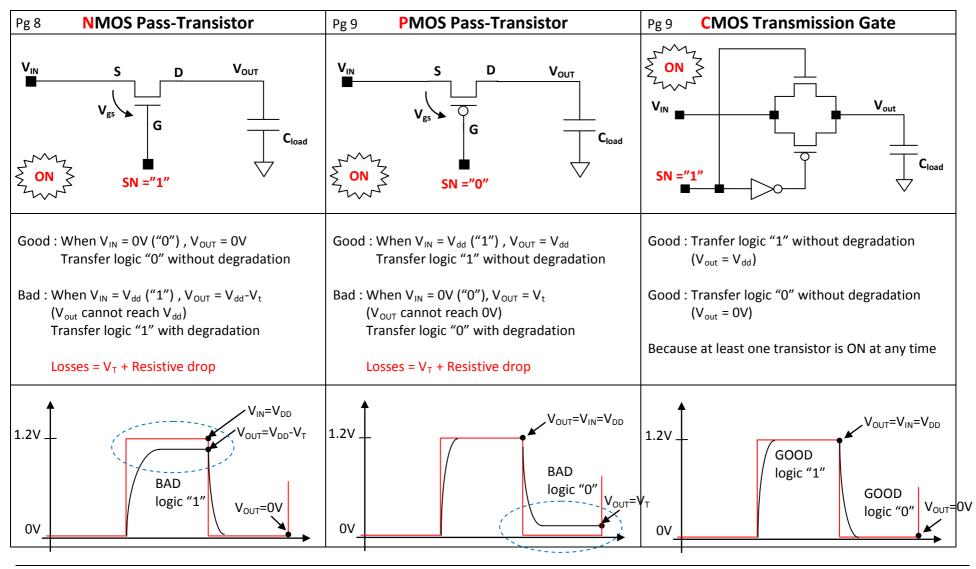

## 3.2.1 NMOS Pass Transistor

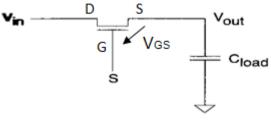

Figure 3-8 NMOS Pass Transistor

Figure 3-8 shows a switch using NMOS transistor. Such switch is known as Pass Transistor. The signal, SN, at the gate of the transistor controls the ON/OFF state of the transistor. When SN = Low, the transistor is OFF and when SN = High ( $V_{dd}$ ), the transistor is ON. In the case of NMOS enhancement transistor, the signal voltage is actually  $V_{gs}$  and it must be greater than  $V_t$ , in order for the transistor to turn ON.

### <u>Operation</u>

(i)  $V_{in}$  = High and  $C_{load}$  is initially uncharged

$C_{\text{load}}$  will start to charge when the switch is ON, however  $V_{\text{out}}$  can only reach  $V_{\text{in}}-V_t$  because exceeding this value, the ON condition will cease to exist and the transistor will turn OFF. Hence, it can be concluded that NMOS transistor transfer logic High with degradation. That is, the  $V_{\text{out}}$  cannot reach full  $V_{\text{in}}$ . The direction of the current flow is from left to right.

### (ii) $V_{in}$ = Low and $C_{load}$ is initially charged to $V_{in}$ - $V_t$

With the switch ON,  $C_{load}$  will start to discharge and the current flows from right to left. This action can continues until  $C_{load}$  discharges to 0V. Thus, NMOS transistor transfers logic Low without degradation.

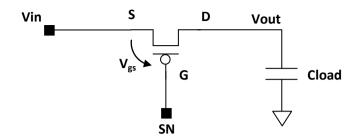

### 3.2.2 PMOS Pass Transistor

Figure 3-9 PMOS Pass Transistor

In PMOS Pass transistor, a logic low signal is applied at SN to turn ON the transistor. Hence, when SN = High ( $V_{dd}$ ), the switch will turn OFF. In the case of PMOS enhancement transistor, the signal voltage,  $V_{gs}$ , must be less than  $V_t$ , in order to turn ON the transistor.

**Operation**

(i)  $V_{in}$  = High and  $C_{load}$  is initially uncharged

With SN = Low such that  $V_{gs} < V_t$ , the transistor is ON and current flows from left to right thus charging  $C_{load}$  to  $V_{in}$ . For PMOS transistor, the transfer of High logic level is without degradation.

(ii)  $V_{in}$  = Low and  $V_{out}$  is initially charged to  $V_{dd}$

Keeping the switch ON,  $C_{load}$  will starts to discharge and current flows from right to left. However,  $C_{load}$  can only discharges until  $V_{out}$  is  $V_t$  because going beyond this will cause the transistor to turn OFF. Hence, PMOS transistor transfers Low logic with degradation.

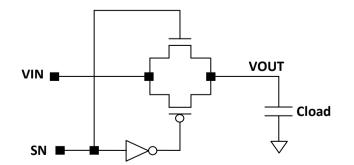

### **3.2.3 CMOS Pass Transistor**

Both NMOS and PMOS devices exhibit poor performance when transmitting one of two logic information. A CMOS switch is made up of a NMOS and an PMOS pass transistor connected in parallel. It is controlled by a pair of complementary signals so that both transistors are either "ON" or "OFF" at the same time.

Figure 3-10 CMOS Transmission Gate

The PMOS transistor can charge  $V_{out}$  to  $V_{dd}$  without degradation while NMOS transistor can discharge  $V_{out}$  to  $V_{ss}$  (0V) without degradation, thus a CMOS transmission gate gives good logic High and logic Low level transmission.

## 3.2.4 Power Supply Voltage

$V_{dd}$  has decreased in modern processes, typical  $V_{dd}$  for 180nm (0.18um) technology ranges from 1.8V to 3.3V. A high  $V_{dd}$  would damage these modern tiny transistors. On the other hand, a lower  $V_{dd}$  saves power.

# **3.3 STATIC CMOS CIRCUITS**

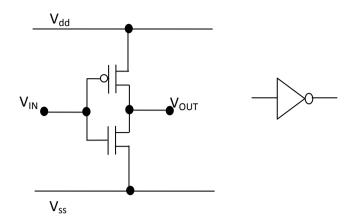

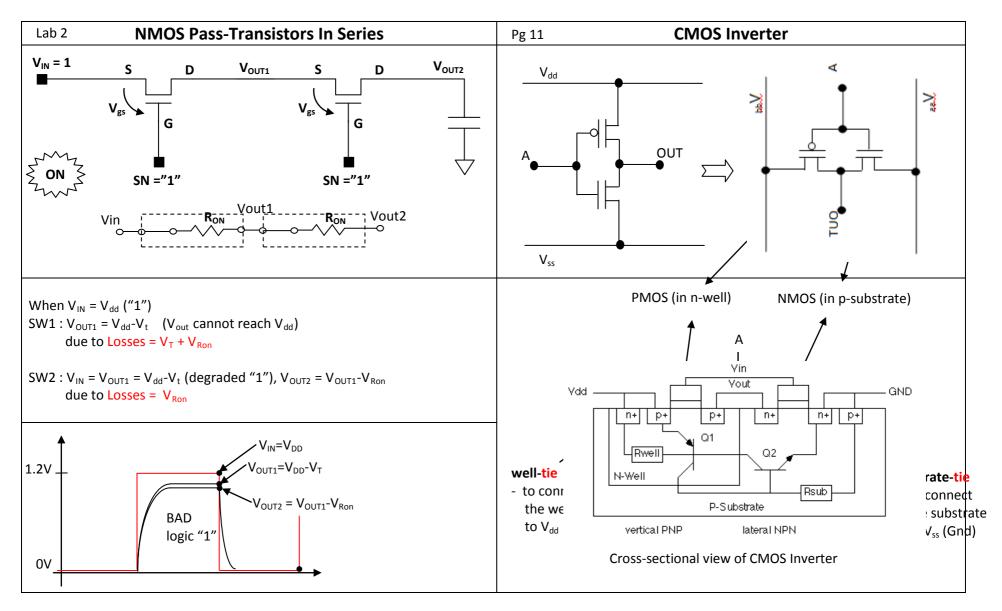

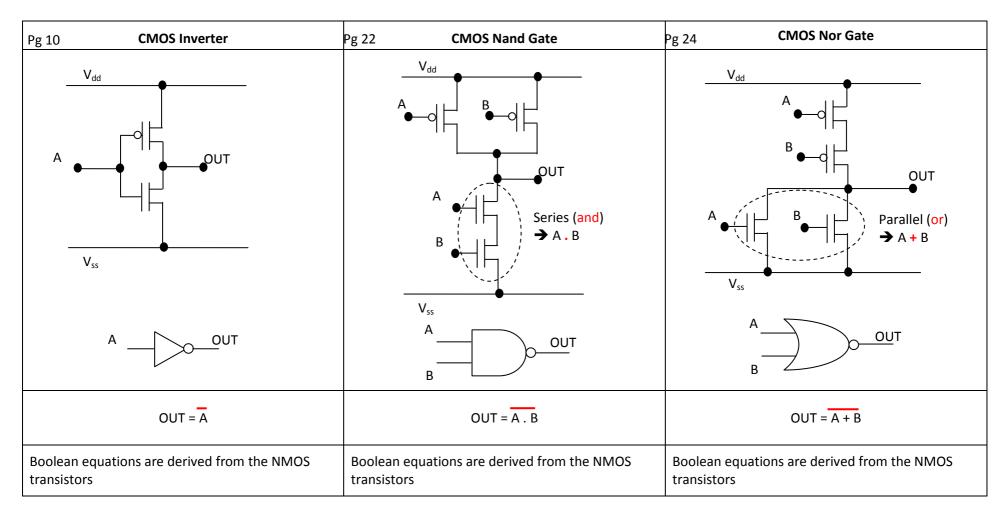

## 3.3.1 CMOS Inverter

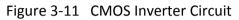

Figure 3-11 shows a CMOS inverter. In this inverter, both NMOS and PMOS transistors are used. The PMOS function as the load while the NMOS function as the driver device.

For a  $V_{in}$  = High, the PMOS transistor will turn OFF and the NMOS transistor will turn ON. Thus, discharging can take place via the pull-down (driver) device and give a logic low output.

Similarly, for a  $V_{in}$  = Low, the PMOS transistor will turn ON while the NMOS transistor will turn OFF, hence the output charges towards  $V_{dd}$  via the pull-up (load) device and gives a logic high output.

CMOS Inverter Circuit (rotated 90°)

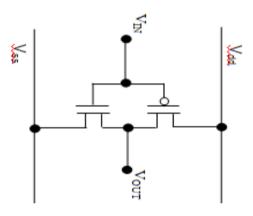

FIGULE 3 12 CLOSS SECTIONAL VIEW OF CIVIOS INVELTED

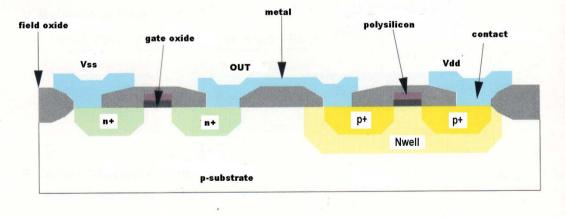

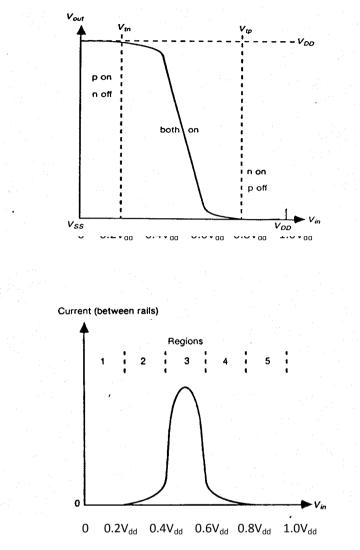

Figure 3-13 shows the amount of current flowing between the supply rails of a CMOS inverter. It can be divided into 5 sub-regions as follows :-

Figure 3-13 CMOS Inverter Current vs Vin

#### Region 1

- $V_{in} = 0.1V_{dd}$ , PMOS fully turned on (Linear) and NMOS is OFF (Cutoff).

- No current flows through the inverter and output is connected to V<sub>dd</sub>.

#### Region 2

- $V_{in}$  is increased to a level greater than  $V_t$  (eg  $V_{in}$ =0.3 $V_{dd}$ ). This causes the NMOS to turn ON in the Saturation mode and the PMOS remains in the Linear mode.

- Small amount of current flows through the inverter.

### Region 3

- With  $V_{in}$  = 0.5 $V_{dd}$ , both NMOS and PMOS transistor operates in the Saturation mode.

Region 4

- With  $V_{in} = 0.7V_{dd}$ , thus  $V_{gs} < V_t$  for PMOS resulting in PMOS operating in the Saturation model while NMOS transistor operates in the Linear mode.

- Output voltage drops close to V<sub>ss</sub>.

#### Region 5

- V<sub>in</sub>= 0.9V<sub>dd</sub>, NMOS is fully turn on (Linear) and PMOS is OFF (Cutoff).

- No current flows through the inverter.

Hence, for CMOS inverter, there is no static current flowing but the inverter draws a high current when the transistors are changing states in Region 3. This current is known as the dynamic current.

## 3.3.2 Switching Time

How fast a logic gate can switch from one logic state to the next depends on its load capacitance and its wiring path resistance. The gate capacitance of the driven stage and other parasitic capacitance along the way constitute the load capacitance. As for the wiring path resistance, it is dependent on the logic state of the logic gate, which in turn determines the path of current flow.

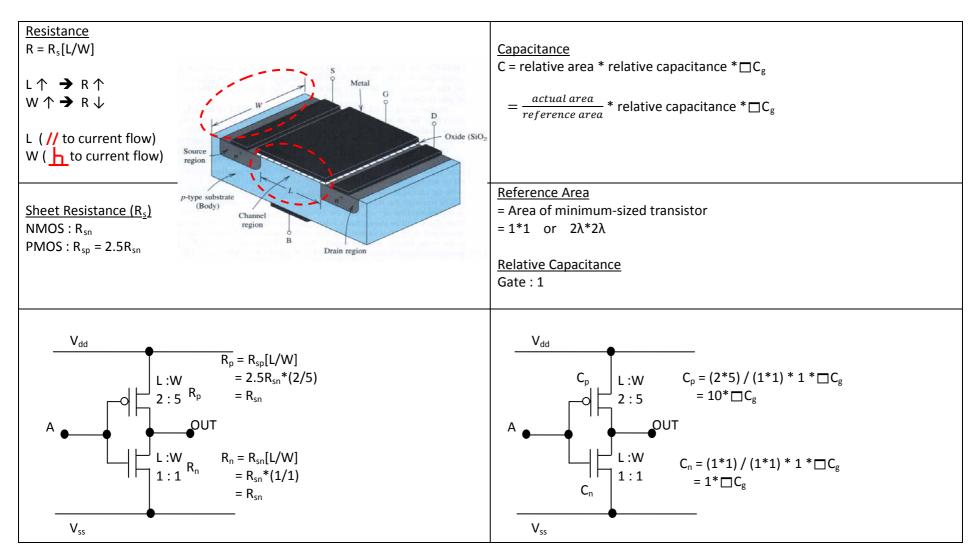

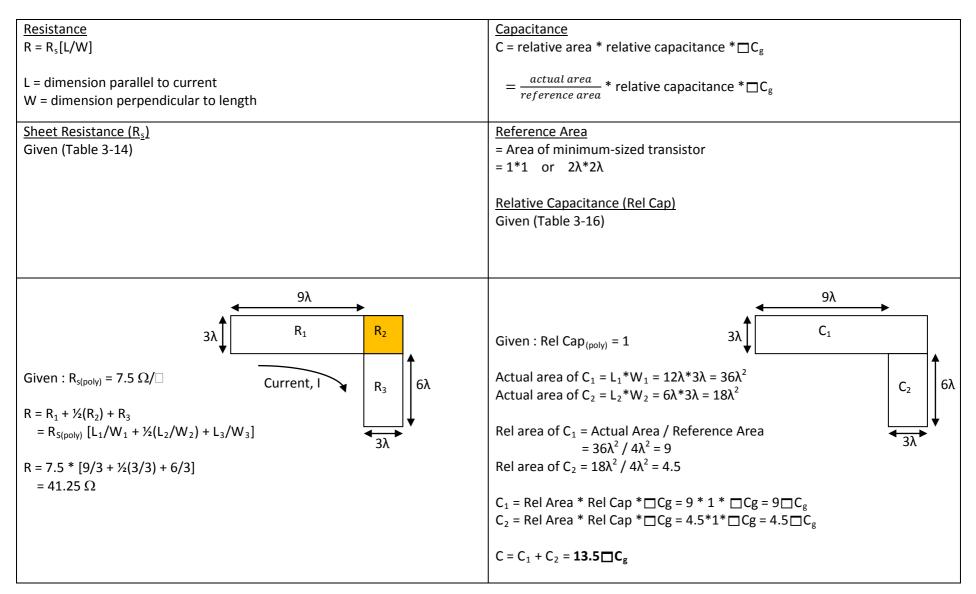

#### **3.3.2.1** Determination of Path Resistance

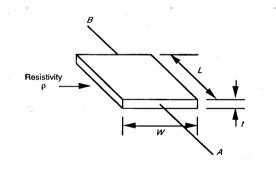

Figure 3-14 Sneet Kesistance Wodel

Resistance of a material is given as:

$$R = \rho L/A$$

$\Omega$

If the material has a sheet resistance of  $R_s = \rho/t [\Omega/\Box]$ , then the resistance of the material can be expressed as :

$$R = R_s(L/W)$$

[ $\Omega$ ]

Table 3-15 gives the sheet resistance of various materials commonly used in the fabrication of MOS integrated circuits.

| Layer /              | Rs [Ω/□]                             |  |

|----------------------|--------------------------------------|--|

| Technology           | (0.18um technology)                  |  |

| Metal1               | 0.01                                 |  |

| N+ Diffusion         | 50 ~ 65                              |  |

| P+ Diffusion         | 155 ~ 173                            |  |

| Polysilicon          | 7.5 ~ 18                             |  |

| n-channel transistor | R <sub>sn</sub>                      |  |

| p-channel transistor | R <sub>sp</sub> ≈ 2.5R <sub>sn</sub> |  |

| Table 3-15 | Typical | $R_s$ Of | MOS | Layers |

|------------|---------|----------|-----|--------|

|------------|---------|----------|-----|--------|

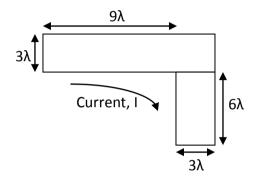

Square corner rectangle is counted as ½ square of resistance

Figure 3-16 MOS Wire Segment

For polysilicon with R<sub>s</sub> = 7.5  $\Omega/\Box$ , the total resistance will be :-R = 7.5 \* (9/3 + ½(3/3) + 6/3) = **41.25**  $\Omega$

### **3.3.2.2 Determination of Load Capacitance**

Capacitance are found between two conducting layers separated by a dielectric  $(SiO_2)$  and is given as :-

$$C = (\varepsilon_o * \varepsilon_r * A) / D$$

Farads

where

$\varepsilon_{o}$  = 8.85 x 10<sup>-12</sup> F/m (permittivity of free space)

$\varepsilon_r$  = relative permittivity of SiO<sub>2</sub> ~ 4.0

A = Area of overlapping conducting layer

Alternatively, capacitance can also be determined using :-

C = relative area \* relative capacitance \*□Cg

where

relative area = ratio of actual area (A) to area of a minimum sizes gate  $\Box C_g$  = gate to channel capacitance of a minimum size MOS transistor of length 2 $\lambda$  and width 2 $\lambda$  (where 2 $\lambda$  is the process technology's minimum feature size) The advantage of using  $\Box C_g$  to determine capacitance is that the absolute value of the capacitance can be easily obtained by substituting the standard value of  $\Box C_g$  of the target process technology into the expression.

| Capacitance<br>(aF / μm <sup>2</sup> ) | Relative<br>Capacitance                                             |

|----------------------------------------|---------------------------------------------------------------------|

| 100                                    | 1.00                                                                |

| 40                                     | 0.40                                                                |

| 100                                    | 1.00                                                                |

| 30                                     | 0.30                                                                |

| 65                                     | 0.65                                                                |

| 15                                     | 0.15                                                                |

| 18                                     | 0.18                                                                |

| 35                                     | 0.35                                                                |

|                                        | (aF / μm <sup>2</sup> )<br>100<br>40<br>100<br>30<br>65<br>15<br>18 |

Note :  $aF = 1 \times 10^{-18} F$

Table 3-17 Typical Area Capacitance Values For 0.18µm Technology

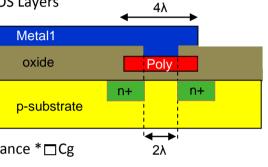

#### (i) Determination of $\Box C_g$ for 0.18µm process technology

$\lambda$  of a MOS transistor using 0.18µm process technology is 0.09µm. Hence, a minimum size MOS transistor of length 2 $\lambda$  and width 2 $\lambda$  for 0.18µm process technology will have a gate area of :-

Gate area =

$$2\lambda * 2\lambda$$

= 0.18 \* 0.18 = 0.0324  $\mu m^2$

For a gate-to-channel capacitance of 100 aF/ $\mu$ m<sup>2</sup>, the standard value of  $\Box C_g$  will be :-

Standard value of  $\Box C_g = 3.24*10^{-2} * 100 \text{ aF}/\mu\text{m}^2$ = 3.24 aF = 3.24 \* 10<sup>-18</sup> F (ii) <u>Multi-layer Capacitance Calculation</u>

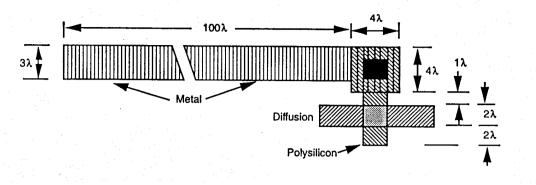

Figure 3-18 Capacitance Between MOS Layers

- Capacitance between Metal and substrate, C<sub>m</sub>

Area of metal =  $100\lambda \times 3\lambda = 300\lambda^2$ Relative area =  $300\lambda^2/4\lambda^2 = 75$

Thus,

$C_m$  = relative area \* relative capacitance \*  $\Box Cg$ = 75 \* 0.3 \*  $\Box C_g$ = 22.5  $\Box C_g$

- Capacitance between Polysilicon and substrate, C<sub>p</sub>

Area of Polysilicon =  $(4\lambda x 4\lambda)$ +  $(1\lambda x 2\lambda)$ + $(2\lambda x 2\lambda)$  =  $22\lambda^2$ Relative area =  $22\lambda^2 / 4\lambda^2$  = 5.5

Thus,

C<sub>p</sub> = 5.5 \* 1 \* □C<sub>g</sub> = 5.5 □C<sub>g</sub>

- Capacitance between gate and channel (diffusion and polysilicon overlap region)

$$C_{g} = 4\lambda^{2} / 4\lambda^{2} * 1* \Box C_{g} = 1 \Box C_{g}$$

Thus, the total capacitance is :-

$$C_{T} = C_{m} + C_{p} + C_{g}$$

= (22.5 + 5.5 + 1)\[C\_{g}

= **29**\[C\_{g}\]C\_{g}

Depending on the technology used, the actual capacitance value will vary. For  $0.18 \mu m$  technology,

# **3.3.3 Delay Calculations**

#### 3.3.3.1 *τ*-Model

In many occasions, a rough timing analysis of circuit is needed before getting into its layout. A simplified model, called the  $\tau$ -model, can provide such estimation. This model is often used to analyze circuit involving a large capacitance load. In such a case, the load dominates, such that the diffusion and wiring capacitance can be ignored. In circumstances when this condition cannot be satisfied, the  $\tau$ -model provides a tool for the designer to gain some insight of the timing relationship in the circuit.

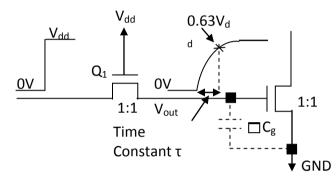

Figure 3-19 Model for Derivation of  $\tau$

Consider a load capacitance of  $1 \square C_g$  being charged through a minimum-sized NMOS transistor to 63% of its final value, as shown in Figure 3-19. The time constant,

or

$$\tau = \mathsf{R}_{\mathsf{s}}\{\mathsf{L}/\mathsf{W}\} \times \mathbb{1} \square \mathsf{C}_{\mathsf{g}}$$

$$\tau = \mathsf{R}_{\mathsf{sn}} \times \square \mathsf{C}_{\mathsf{g}}$$

$\tau = RC$

Since  $\tau$  is calculated in terms of  $R_{sn}$  and  $\Box C_g$ , which are fixed for each technology, thus for each process technology  $\tau$  is a constant.

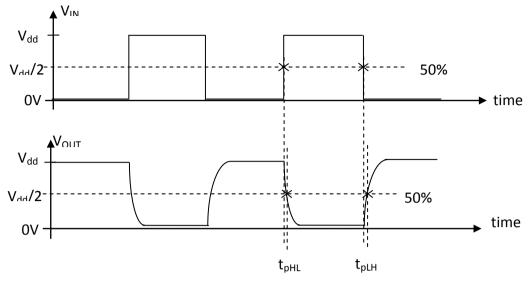

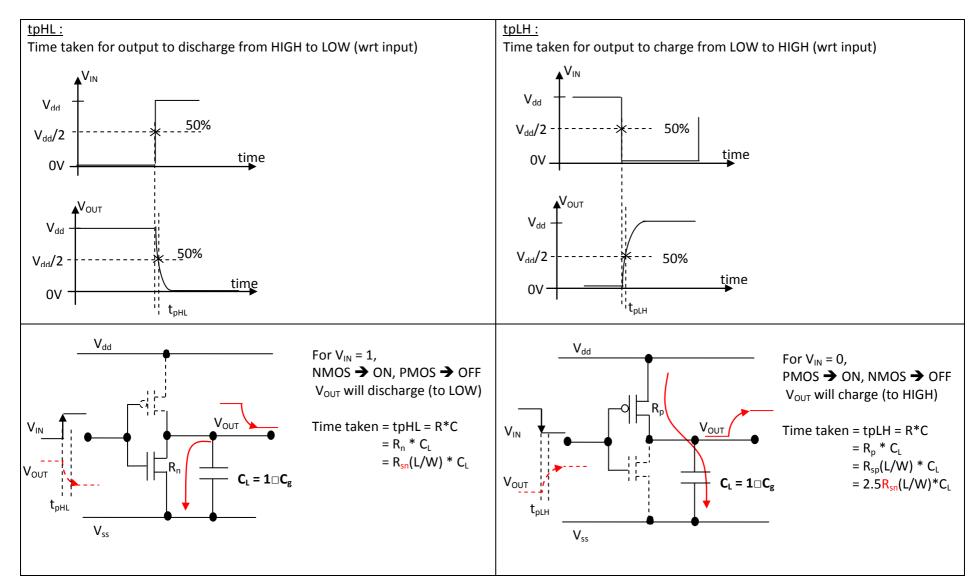

#### 3.3.3.2 Propagation Delay

Propagation delay, symbolized by  $t_p$ , is the time required for a digital signal to travel from the input of a logic gate to the output. The average time needed for the output to respond to a change in the input logic state is defined as :

$$t_p = \frac{t_{pHL} + t_{pLH}}{2}$$

where  $t_{pHL}$  = propagation delay for a *High* to *Low* transition at the output  $t_{pLH}$  = propagation delay for a *Low* to *High* transition at the output

Figure 3-20 Propagation Delay

The timings are measured from the reference voltage of  $V_{dd}/2$  at the input to the reference voltage of  $V_{dd}/2$  at the output.

Assuming ideal input signal, the high to low propagation delay,  $t_{pLH}$ , can be derived by considering the time taken to charge the capacitance,  $C_L$ , from OV to  $V_{dd}/2$  and the low to high propagation delay,  $t_{pHL}$ , be the time taken to discharge  $C_L$ , from  $V_{dd}$ to  $V_{dd}/2$ . Since the transition point of is  $V_{dd}/2$ , which is close to 0.63V<sub>dd</sub>, *it is a common practice to use propagation delay and time constant interchangeably*.

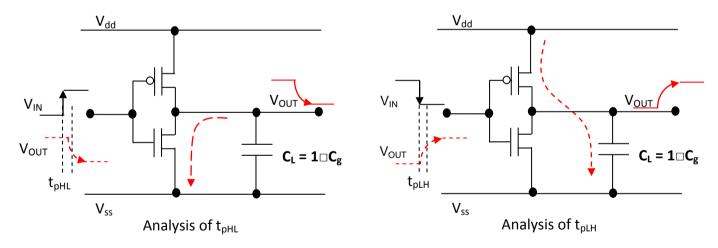

Figure 3-21  $t_{pHL}$  and  $t_{pLH}$  Analysis

For a CMOS inverter with transistors of minimum size, that is L:W = 1:1, driving a load of  $1\square C_g$  , the

$$t_{\text{pLH}} \approx R_{\text{p}} C$$

As the mobility of electrons,  $\mu_n$ , is ~2.5 times the mobility of holes,  $\mu_p$ ; for PMOS and NMOS of the same W & L ratio, the PMOS transistor will have about 2.5 times lesser

current flowing through it under the same operating conditions, resulting in  $R_{p}\approx 2.5R_{n}.$  Hence,

$$t_{pLH} \approx R_p C$$

$$\approx 2.5 R_{sn} * \Box C_g$$

$$\approx 2.5 \tau$$

$$t_{pHL} \approx R_n C$$

$$\approx R_{sn} * \Box C_g$$

$$\approx \tau$$

= 1.75 T

Thus, t<sub>p</sub> = 1.75 τ.

To obtain a  $t_{pLH} \approx t_{pHL}$ , it is necessary to adjust  $W_p \approx 2.5 W_n$  so that current passing through the PMOS is about the same as that flowing through NMOS transistor.

Typical electron mobility for Si at room temperature (300 K) is 1400 cm<sup>2</sup>/ (V·s) and the hole mobility is around 450 cm<sup>2</sup>/ (V·s).

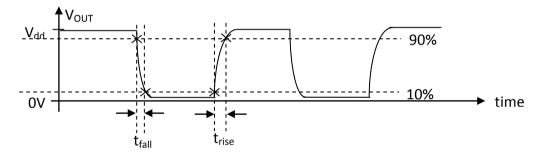

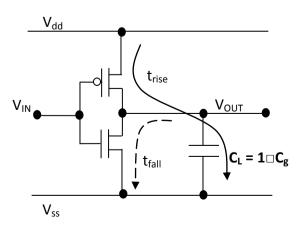

#### 3.3.3.3 Rise and Fall Time

Rise time,  $t_{rise}$ , is the time taken to charge  $V_{out}$  from 10% to 90% of  $V_{dd}$  while fall time,  $t_{fall}$ , is the time taken to discharge  $V_{out}$  from 90% to 10% of  $V_{dd}$ .

Figure 3-22 Rise and Fall Time

Taking a simplified view where a CMOS inverter charges towards  $V_{dd}$  and the p-transistor stayed in saturation while the n-transistor is fully off for the entire charging period of the load capacitor,  $C_L$ ,

Rise time can be estimated to be :

and

$V_{out} = \frac{I_{ds(sat)} t}{C_L}$  $I_{ds(sat)} = \frac{K_p}{2} \left(\frac{W_p}{L_p}\right) \left(\left|V_{gs}\right| - \left|V_{tp}\right|\right)^2$

thus,

$t_{rise} \approx 3.7^* C_L / (\beta_p V_{dd}) \qquad -- (1)$

$t_{fall} \approx 3.7^* \ C_L \ /\beta_n \ V_{dd}) \qquad -- (2)$

where

$\beta_p = \mu_p \epsilon_{ox} / t_{ox} [W_p / L_p]$ C<sub>L</sub> = load capacitance

Similar reasoning can be applied to the discharge of  $C_L$ , through the n-transistor, to  $V_{ss}$ . Assume the p-transistor is off and n-transistor is on during this period, thus

Fall time can be estimated to be [I=C.dv/dt]:

where

$$\beta_n = \mu_n \epsilon_{ox} / t_{ox} [W_n / L_n]$$

The ratio of expression (1) and (2) with  $\mu_n \approx 2.5\mu_p$ , results in  $\beta_n \approx 2.5\beta_p$ . That is, when a gate uses transistors of the same size (L & W) for both NMOS and PMOS, it will experience a  $t_{rise} \approx 2.5 t_{fall}$ . In order to achieve symmetrical operation using minimum channel length, make  $W_p \approx 2.5W_n$ .

#### 3.3.3.4 Maximum Switching Frequency

The sum of transient time  $(t_{rise} + t_{fall})$  represents the minimum time needed for a gate to undergo a complete cycle, ie. for the output to change from a logic 1 to logic 0 voltage and then back to logic 1 value. Thus, maximum switching frequency can be defined as :-

$$f_{max} = \frac{1}{t_{rise} + t_{fall}}$$

This frequency also represents the maximum rate of data transfer for the gate. In system design, the working value of  $f_{max}$  is set by the slowest gate or datapath element in the network.

#### 3.3.3.5 CMOS Inverter Characteristics Summary

#### (i) Power Consumption

When the CMOS inverter is in a steady state, regardless of the output state, only half of the circuit is conducting and there is no closed path between  $V_{dd}$  and  $V_{ss}$ . Since no current flows, the steady state power is OW. That is, there is no static power dissipation.

When the CMOS inverter is in transition from one state to another, there is a window where both the transistors are turned on, so a current flows between  $V_{dd}$  and  $V_{ss}$  through them. This is called the short-circuit current, which contributes to the dynamic power dissipation in the CMOS inverter.

A well-designed circuit operating with well-behaved signals of reasonably fast rise and fall time would go through the transition quickly. This dynamic power dissipation is thus less significant compared to the power caused by current that flows through the transistors to charge or discharge a load capacitance,  $C_L$ .

(ii) Ratio-less Device

$V_{OUT}$  of the CMOS inverter is able to give a full voltage swing from  $V_{dd}$  to  $V_{ss}$  regardless of the relative dimensions of the PMOS and NMOS transistors. Thus CMOS devices are sometimes known as ratio-less devices.

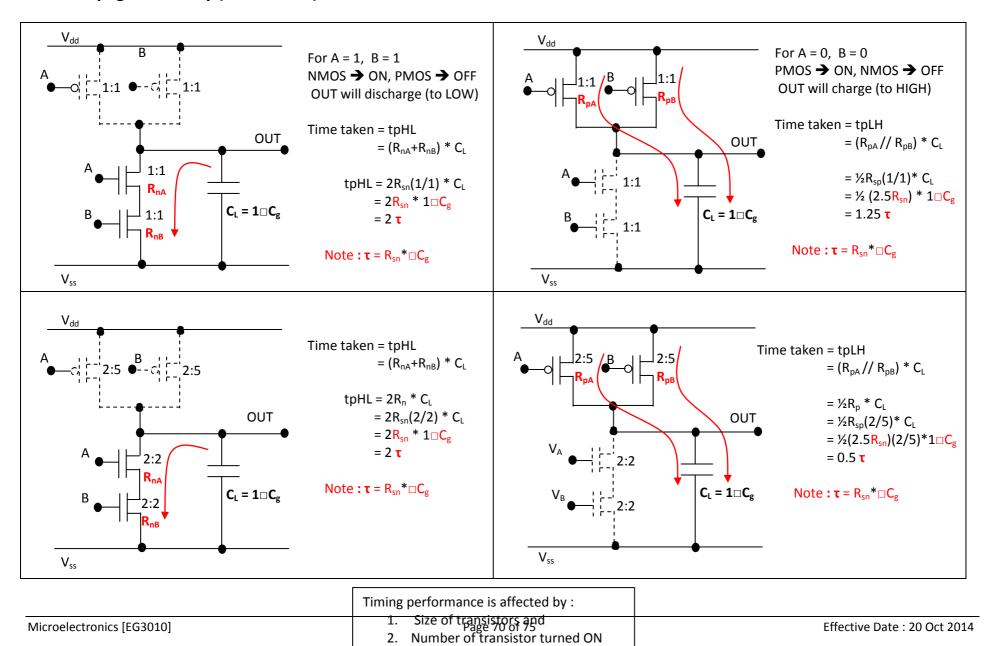

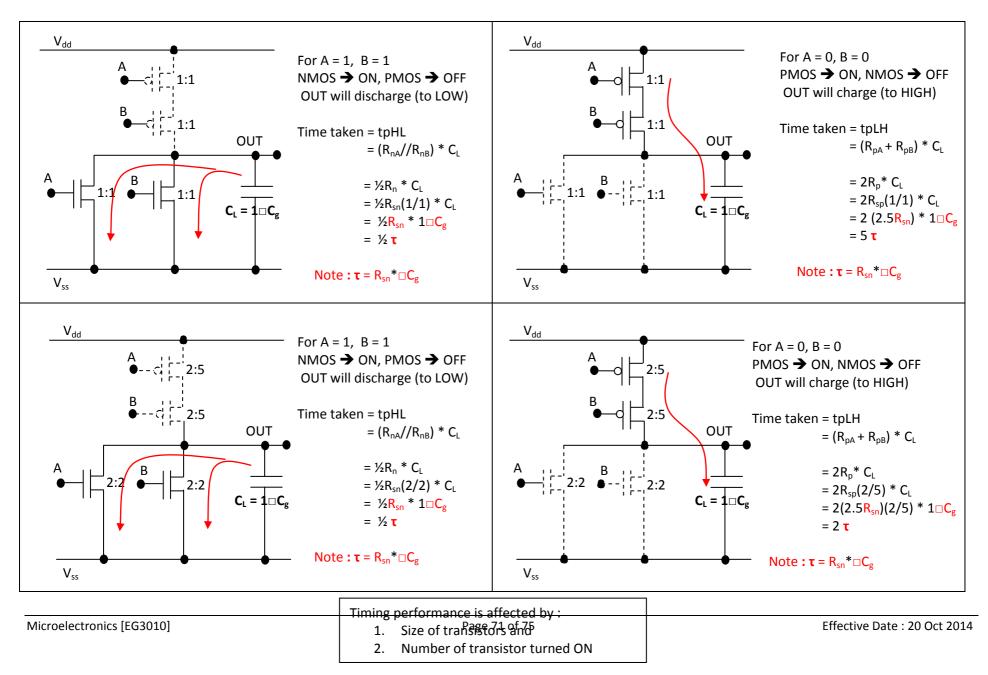

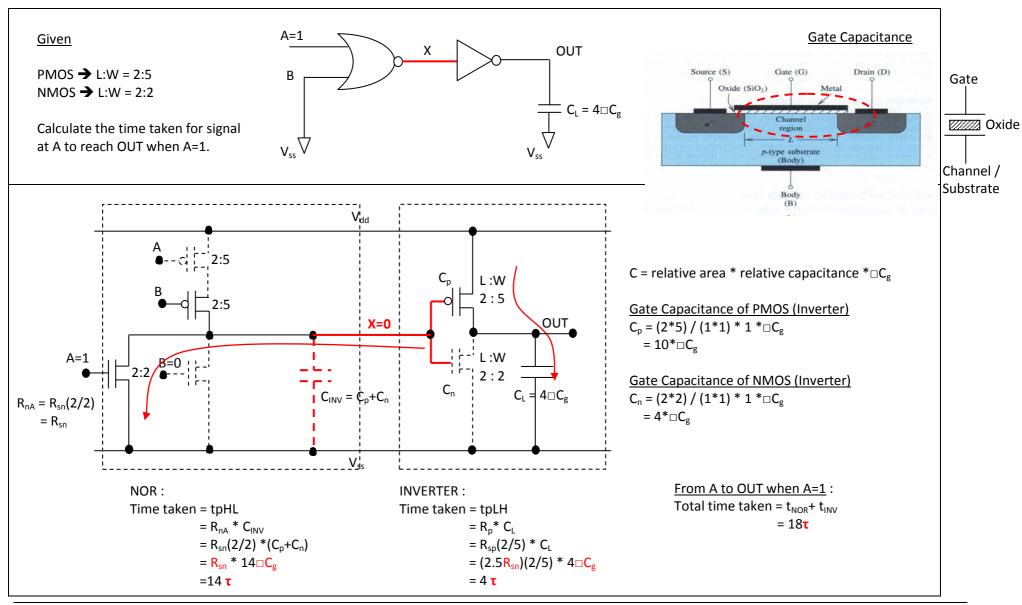

(iii) Timing Performance

Ratios introduced in CMOS gates are for the purpose of improving the timing aspects of the gates. Timing performance is affected by the size of the transistors and the number of transistor turned ON, to achieve the desired output state.

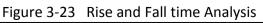

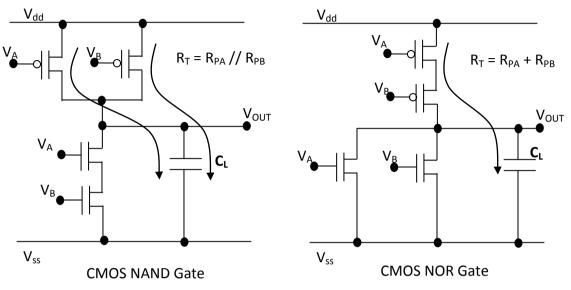

### 3.3.4 CMOS NAND Gate

For CMOS, the pull-up PMOS transistors and the pull-down NMOS transistors form a complementary set. The pull-up transistors act as loads and are complementary in connections to the pull-down NMOS devices. The pull-down devices, in turn, determine the output function.

When the pull-down devices are connected in series, an ANDed function is achieved and when they are connected in parallel, an ORed function is achieved. The connection shown in Figure 3-24 gives a NAND output.

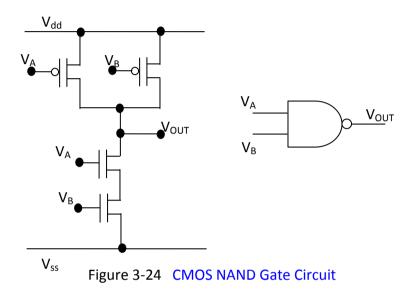

### 3.3.5 CMOS NOR Gate

In the case of a NOR gate, the pull-down transistors are connected in parallel. Hence, the pull-up transistors will be connected in series. With the pull-down transistors in parallel, the effect is that of an ORed function. The connection shown in Figure 3-25 gives a NOR output.

Figure 3-25 CMOS NOR Gate Circuit

## 3.3.6 NAND and NOR Gate Delays

#### (i) <u>Low-to-High Delay (t<sub>pLH</sub>)</u>

The  $t_{pLH}$  of the NAND gate depends on the number of p-transistors that are connected in parallel (number of inputs) while that of a NOR gate depends on the number of p-transistors that are connected in series.

Figure 3-26 Direction of current flow during  $t_{pLH}$

Figure 3-26 shows a 2-input NAND gate and a 2-input NOR gate. Assuming that all the transistors are minimum-sized transistors, the total resistance experienced by the NAND gate during the low-to-high transition is  $R_{sp}$  [L/W] or less while that experienced by the NOR gate is 2 \*  $R_{sp}$  [L/W]. Hence, the  $t_{pLH}$  of the NOR gate will be at least 2 times greater than that of the NAND gate.

#### (ii) <u>High-to-Low Delay (t<sub>pHL</sub>)</u>

The  $t_{pHL}$  of the NAND gate depends on the number of n-transistors that are connected in series (number of inputs) while that of a NOR gate depends on the number of n-transistors that are ON.

As shown in Figure 3-27, assuming that all the transistors are minimum-sized transistors, the total resistance experienced by the NAND gate during the high-to-low transition is 2 \*  $R_{sn}$  [L/W]. For NOR gate, the  $t_{pHL}$  resistance depends on the number of n-transistors that are ON, which is  $R_{sn}$ [L/W] or less.

Figure 3-27 Direction of current flow during  $t_{pHL}$

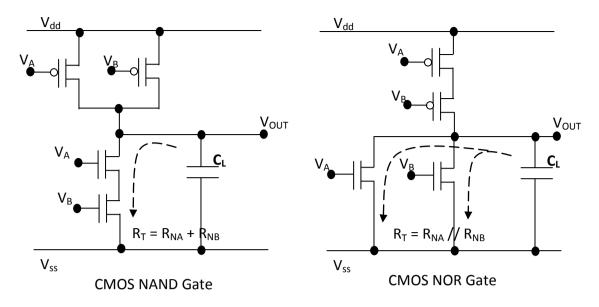

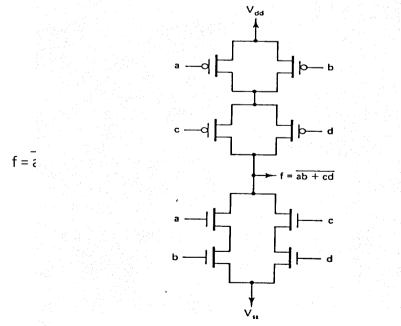

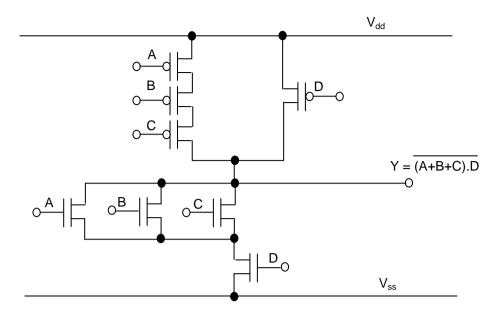

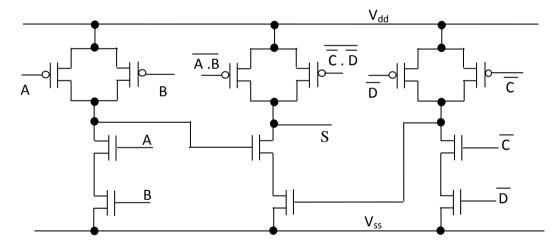

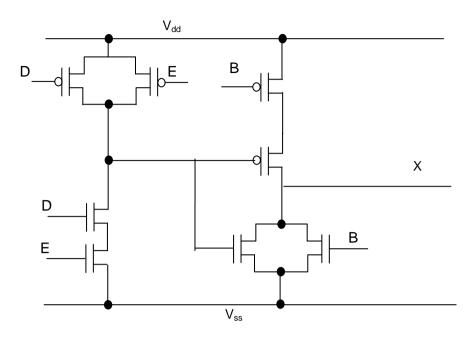

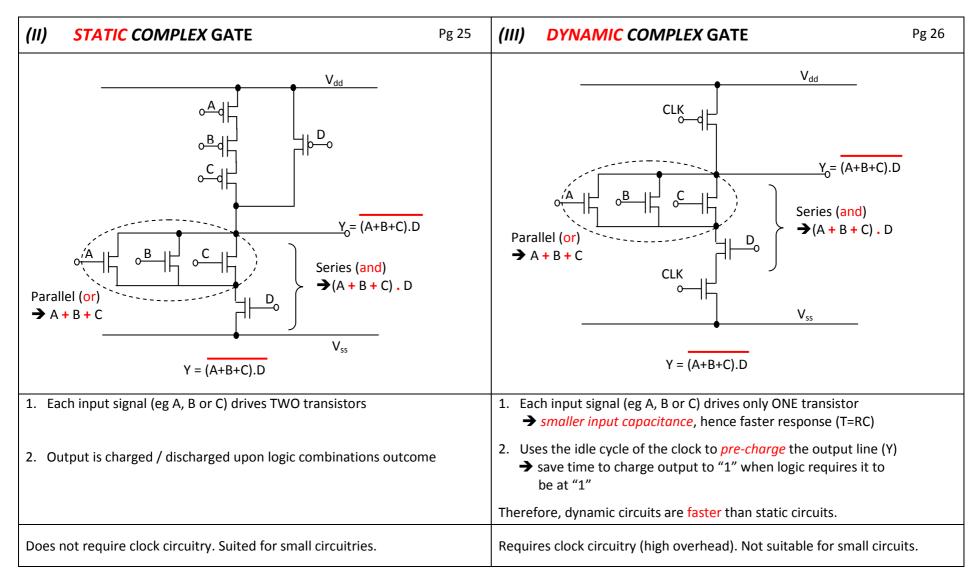

# 3.3.7 CMOS Complex Implementation

For the circuit shown in Figure 3-28, pull-up PMOS transistors and the pull-down NMOS transistors form a complementary set. The pull-up transistors act as loads and are complementary in connections to pull-down NMOS devices. The pull-down devices, in turn, determine the output function.

Input *A* and *B* are in series, hence they are *AND* together. Similarly, input C and D are also ANDed together. As the *AB* branch and *CD* branch are in parallel, the two branches are hence *OR*ed together. Thus, the output function of the complex implementation is :-

Figure 3-28 Complex Gate CMOS Implementation

Figure 3-29 Complex Gate CMOS Implementation

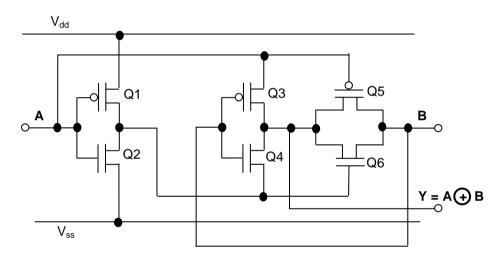

Figure 3-30 Complex Gate Implementation (XOR)

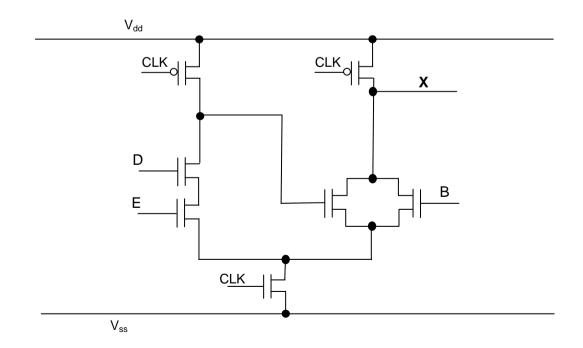

# 3.4 DYNAMIC MOS CIRCUIT

Dynamic MOS circuits work on the principle of turning transistors ON or OFF under clock control. Basically, a p-transistor is used for the non-time-critical precharging of the output line so that the output capacitance is charged to  $V_{dd}$  during the OFF period of the clock signal  $\phi$ . During the same period (next half cycle), the inputs are applied to the n-block and the state of the logic is then evaluated.

Such circuit can operates at a higher speed compared to the static circuits as input capacitance of dynamic gate is smaller. With precharging (discharging) of the output line, the amount of time needed for the output to change from one state to another is also reduced significantly.

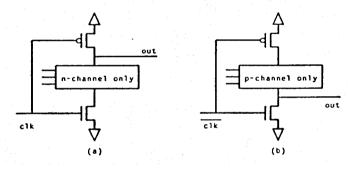

# 3.4.1 P-E (Precharge-Evaluation) Logic

This logic works on one clock signal and two separate devices, the p-transistor and the n-transistor. Figure 3-31(a) shows a PE logic using n-channel transistor as the evaluation transistors while Figure 3-31(b) shows a PE logic using p-channel transistors as the evaluation transistors.

Figure 3-31 P-E Logic Gate

There are two phases to their operation, namely the precharge phase and the evaluation phase. With reference to Figure 3-31(a),

#### Precharge Phase

Precharging is done when the *clk* signal is Low. During which the n-transistor is OFF and the p-transistor is ON. This causes the output to be precharged HIGH. For logic using n-channel evaluation gates, its output must be connected only to p-channel based gates for correct precharging.

#### Evaluation Phase

Evaluation of logic is done when the *clk* signal goes High. When the *clk* signal goes High, the p-transistor turns OFF while the n-transistor goes ON. This provides a path to  $V_{ss}$ . Depending on the logic of the evaluation transistors, the charges on the output line may either be discharged or remains.

When using a single phase clock, dynamic logic structure of the same type cannot be cascaded since, owing to circuit delays, an incorrect input to the next stage may be present when evaluation begins. One remedy is to alternate the structure.

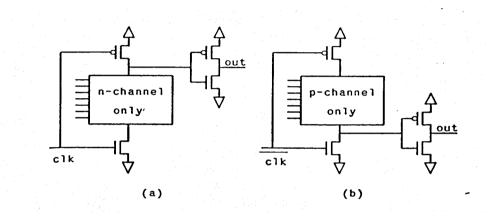

# 3.4.2 Domino Logic

This logic consists of two basic elements, namely the PE gate and an inverter at the output. The inverter at the output acts as a buffer to increase the driving capability of the gate. This logic supports single phase clock with cascading of logic structures of the same type. That is, it enables its output to be connected to similar type of (n-type or p-type) gates, yet achieve proper precharging of the output lines.

Figure 3-32 Domino Logic Gate

# 3.5 MOS CIRCUIT PERFORMANCE

The electrical behavior of a MOS transistor is primarily determined by its gain factor,  $\beta$ , its threshold voltage  $V_T$  and its body factor, K. Generally, the values of these parameters are largely dependent on the width, W and length L of a transistor. The influence of these dependencies is particularly significant in submicron and deep submicron MOS processes.

# **3.5.1** Scaling of MOS Devices

Over the past decades, scaling of CMOS devices has yield tremendous gains in chip performance and functionality. Scaling refers to the systematic reduction of transistor dimensions from one generation to the next, reducing the parasitic capacitances and also the carrier transit times in the devices. One result of this scaling is an improvement in circuit speed; this improvement is quite dramatic in the case of MOS-based circuits. Another result of scaling is that it narrows the performance gap between CMOS and logic gates based on bipolar transistors. Finally, reduction of transistor dimensions improves the packing density of CMOS.

#### 3.5.1.1 Full Scaling of MOS devices

There are many possible schemes for scaling CMOS. Of these, the most obvious approach is "full scaling" which involves scaling all dimensions and voltages by the same factor, 1/s, where s is greater than one. The key dimensions to scale are gate dimensions and oxide thickness; the key voltage to scale is the supply voltage. The motivation for scaling the voltage is that this will leave the electric field intensities unchanged, thus avoiding breakdown effects.

#### **3.5.1.2 Constant Voltage Scaling of MOS devices**

Another approach is called "constant voltage scaling". This involves scaling all dimensions by the factor, 1/s while keeping all voltages constant. Although constant voltage scaling increases the electric filed intensities in the devices, its advantages includes allowing the same supply voltage from one generation to the next and better speed performance. However, the disadvantage is that the electric field increases as the minimum feature length is reduced. This leads to velocity saturation, mobility degradation, increased leakage currents and lower breakdown voltages.

| Parameter            | Symbol          | Constant<br>Field<br>Scaling | Constant<br>Voltage<br>Scaling | Constant<br>Voltage Scaling<br>with velocity<br>saturation |

|----------------------|-----------------|------------------------------|--------------------------------|------------------------------------------------------------|

| Gate length          | L               | 1/α                          | 1/α                            | 1/α                                                        |

| Gate width           | W               | 1/α                          | 1/α                            | 1/α                                                        |

| Field                | ω               | 1                            | α                              | α                                                          |

| Oxide<br>thickness   | t <sub>ox</sub> | 1/α                          | 1/α                            | 1/α                                                        |

| Substrate<br>doping  | Na              | α <sup>2</sup>               | $\alpha^2$                     | α <sup>2</sup>                                             |

| Gate<br>capacitance  | C <sub>G</sub>  | 1/α                          | 1/α                            | 1/α                                                        |

| Oxide<br>capacitance | Сох             | α                            | α                              | α                                                          |

| Transit time         | t,              | $1/\alpha^2$                 | $1/\alpha^2$                   | 1/α                                                        |

| Transit<br>frequency | fr              | α                            | $\alpha^2$                     | α                                                          |

| Voltage              | V               | 1/α                          | 1                              | 1                                                          |

| Current              | Ι               | 1/α                          | α                              | 1                                                          |

| Power                | Р               | $1/\alpha^2$                 | α                              | 1                                                          |

| Power-delay          | $P \  \Delta t$ | $1/\alpha^3$                 | 1/α                            | 1/α                                                        |

Figure 3-33 Comparison of the effect of scaling on MOSFET device parameters

## 3.5.2 Channel Length Modulation

Channel length modulation is the shortening of the length of the inverted channel region, beyond the pinch-off point, with increase in drain bias. As the drain voltage increases, the length of the channel shortens further, causing the channel resistance to decrease, hence an increase in current. The effect is more pronounced in transistors of small feature size.

Figure 3-34 Effects of V<sub>ds</sub> on I<sub>ds</sub> in Saturation Region

The saturation current,  $I_{ds}$ , for devices experiencing channel length modulation is given as :-

$$I_{ds} = {K_n/2}[W/L](V_{gs}-V_t)^2(1 + \lambda V_{ds})$$

where

$\lambda$  is the empirical channel length modulation factor;  $\lambda^{\sim}\,0.03/V$

### **3.5.3** Threshold Voltage

One of the parameter that determines the amount of drain current in a MOS transistor is the threshold voltage. It can be seen that higher the threshold voltage, lower will be the device current and hence slower will be the performance.

This voltage is not a constant but is affected by :-

- (i) body effect.

- (ii) hot carrier effect.

#### 3.5.3.1 Body Effect

Normally, the substrate (B) of a NMOS device is biased to  $V_{ss}$  while substrate of a PMOS device is normally biased to  $V_{dd}$ . Hence, the back-bias voltage,

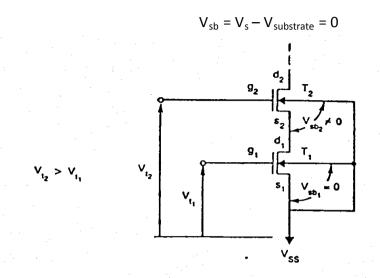

Figure 3-35 NMOS in Series Resulting in Different V<sub>sb</sub> Biasing

When two devices are connected is series (e.g. NAND gate), their  $V_{sb}$  will be different, that is,  $V_{sb1} = 0$  but  $V_{sb2} \neq 0$ . With  $V_{sb2} \neq 0$ , an increase in the thickness of the depletion region under the channel of  $T_2$  will occur. The increased depletion layer requires additional charge. The channel charge therefore decreases if  $V_{gs}$  is held constant. The channel conductivity can only be maintained if  $V_{gs}$  is increased. That is, threshold voltages of  $T_2$  to  $T_1$  is such that  $V_{t2} > V_{t1}$  so as to get same amount of current to flow through  $T_1$  and  $T_2$ . In other words, the threshold voltage is related to the back-bias voltage,  $V_{sb}$  and  $T_2$  is said to be experiencing body effect. It causes MOS transistors of the same type and dimensions to have different threshold voltages.

$$V_T = V_x + K_{\sqrt{V_{sb} + 2\phi_f}}$$

$$V_{T0} = V_x + K_{\sqrt{2\phi_f}}$$

where  $V_x$  = process-related constant threshold voltage

$V_T = V_T |_{V_{sb=0V}}$  K = process parameter, also known as body factor  $V_{sb}$  = source-bulk (back-bias) voltage  $2ø_f$  = band bending where inversion first occurs

If a device was biased without the bulk node connected then a change in operating point could take the device out of its saturation region and significantly change the circuit performance. The bulk voltage is thus a very important parameter in circuit applications and therefore it is best to connect the bulk to the device source connection.

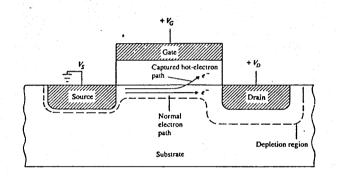

#### 3.5.3.2 Hot-Carrier Effect

Hot carrier effect is the trapping of high energy (hot) carriers in the gate oxide. Such carriers may be injected from the substrate or the channel into the gate oxide. This effect is more likely to occur when the drain to source ( $V_{ds}$ ) voltage is large or when the substrate is heavily doped (excess carriers). These trapped electrons cause shifts in the threshold voltage and reliability problems in the IC chip.

Lightly doped drain (LDD) structure is used to suppress hot carrier effect, particularly in modern devices where the channel length is getting shorter (<2 $\mu$ m). Reduction in power supply voltage also reduces hot carrier effect.

In LDD structure, the presence of spacer nitride results in the source & drain regions being further away from the gate, effectively reduces the source-drain bias induced electric field, thus suppressing the hot carrier effect.

Figure 3-36 Channel Electrons Injected Into the Oxide

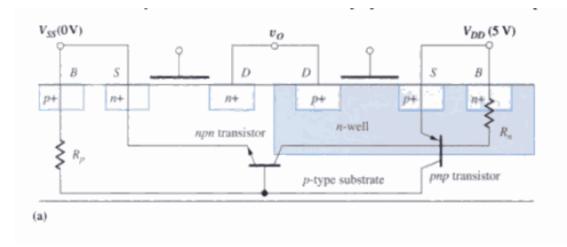

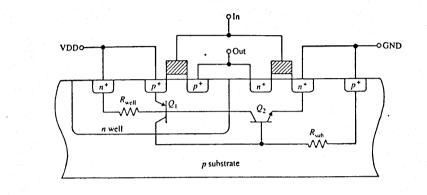

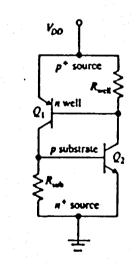

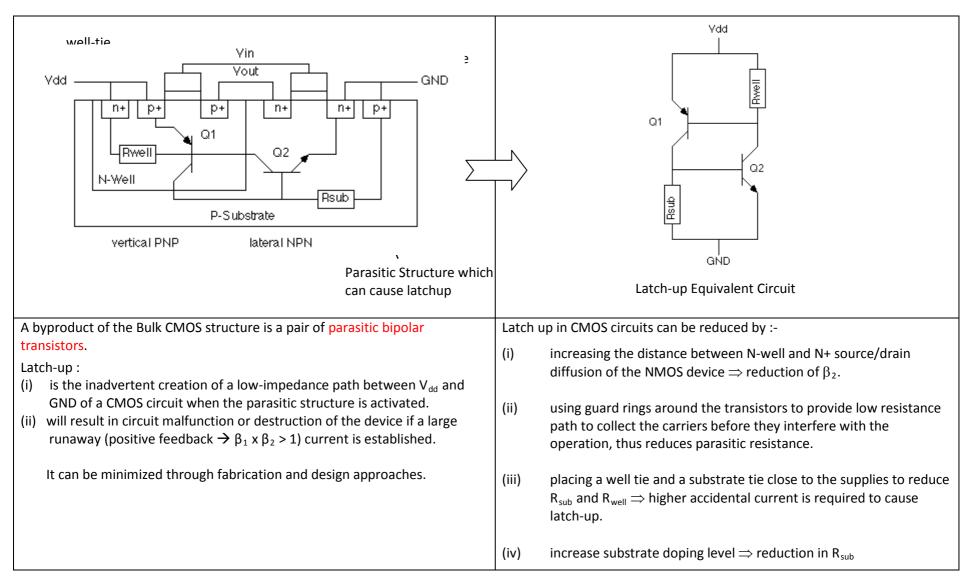

# 3.5.4 CMOS Latchup

Latch up is the inadvertent creation of a low-impedance path between the power supply rails of a CMOS circuit. It occurs when the parasitic structure within the CMOS circuit is activated thus disrupting proper functioning of the part and possibly even leading to circuit destruction due to over-current. A power cycle is required to correct this situation.

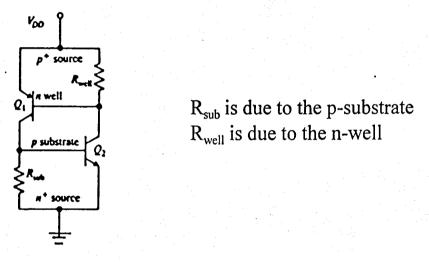

Figure 3.37 shows the parasitic structure. Its silicon-controlled rectifier (SCR) equivalent is shown in Figure 3.38. In the structure, the collector of each BJT is connected to the Base of the other transistor in a positive feedback structure. The parasitic structure is normally dormant under normal operating condition. However, it can be activated when transients occur.

Transients may occur internally during power up or externally due to operating the device beyond its normal operating range. When these transients occur, transistors  $Q_1$  and  $Q_2$  may become forward biased and hence forming a closed loop. A high current can now flow between  $V_{dd}$  and  $V_{ss}$ , and destroy the device in the process.

A scenario of latch-up is when sufficient current flows through  $R_{sub}$ , this in turn causes  $Q_2$  to turn ON. With  $Q_2$  ON, current will be drawn through  $R_{well}$ . If sufficient voltage develops across  $R_{well}$ ,  $Q_1$  can then turn ON, causing more current to flow

rigure 5-38 Laton-up equivalent Circuit

#### 3.5.4.1 Methods to reduce possibility of latch-up

Latch up in CMOS circuits can be reduced by :-

- (i) increasing the distance between N-well and N+ source/drain diffusion of the NMOS device  $\Rightarrow$  reduction of  $\beta_2$ .

- (ii) using guard rings around the transistors as shown in Figure 3.39. For an n<sup>+</sup> guard ring, it provides a low resistance path to collect holes before they interfere with the operation of other circuits outside the guard ring, thus reduces parasitic resistance.

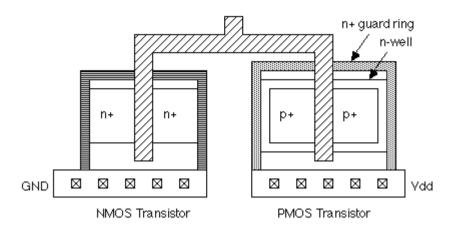

Figure 3-39 CMOS circuit with guard rings

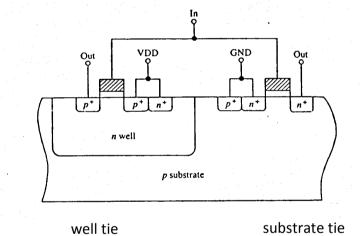

(iii) placing a well tie and a substrate tie close to the supplies. These will in turn reduce the value of  $R_{sub}$  and  $R_{well} \Rightarrow$  higher accidental current is required to cause later we

Figure 3-40 CMOS structure with well tie and substrate tie

(iv) increase substrate doping level  $\Rightarrow$  reduction in  $R_{sub}$

# 3.6 BICMOS DIGITAL DESIGN

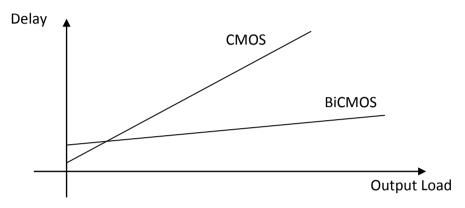

BiCMOS technology combines the advantages of Bipolar and CMOS technology. It retains the low power consumption advantage of CMOS technology and the high drive capability of Bipolar technology.

The timing of such technology is also less sensitive to temperature variations. However, the process complexity is increased.

Figure 3-41 Delay vs Output Load

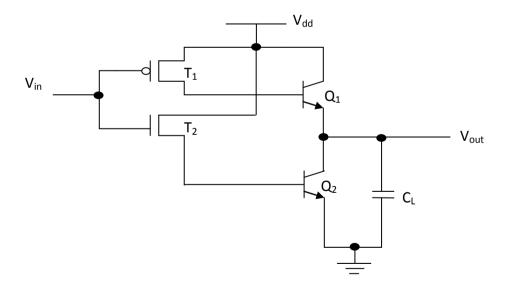

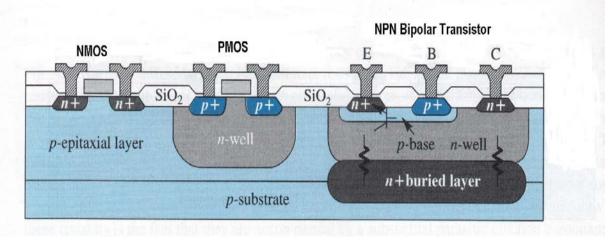

Figure 3-42 shows a BiCMOS inverter circuit and Figure 3-43 shows its cross sectional view on a wafer.

Figure 3-42 Example of a BiCMOS Inverter Circuit

#### Operation of the BiCMOS inverter

- (i) <u>When  $V_{in} = High</u>$ ,</u>

- $T_2$  turns ON,  $T_1$  is OFF

- With  $T_2$  ON,  $Q_2$  also comes ON thus allowing  $C_L$  to discharge to a low value and hence  $V_{out}$  = Low. As in bipolar technology,  $V_{OL}$  is in the range of 0.2V to 0.3V.

- (ii) <u>When V<sub>in</sub> = Low</u>

- $T_1$  turns ON, and  $T_2$  turns OFF

- With  $T_1$  ON,  $Q_1$  also comes ON thus allowing  $C_L$  to charge to a high value of

Figure 3-43 Cross-Sectional structure of Bi-CMOS Process Wafer

# 3.7 CMOS FABRICATION PROCESS

There are many processes available for the fabrication of CMOS circuitries.

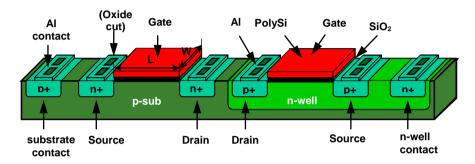

## 3.7.1 N-well Process

The substrate material is of p-type. P-channel (PMOS) transistor is found inside the N-Well region. This method enables sharing of process steps with NMOS fabrication process.

Figure 3-44 Cross-sectional structure of N-Well CMOS Inverter

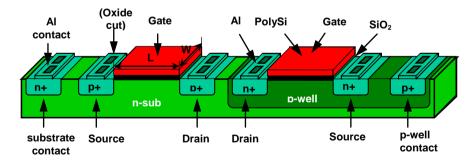

### 3.7.2 P-well Process

The substrate is of n-type. For this process, n-channel (NMOS) transistors are found in the P-Well regions.

Figure 3-45 Cross-sectional structure of P-Well CMOS Inverter

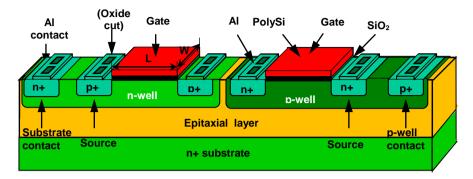

### 3.7.3 Twin-tub Process

For this process, both P-well and N-well are formed on the substrate, thus the substrate can be of p-type or n-type. This process requires more processing steps but it provides better optimisation of performance.

Figure 3-46 Cross-sectional structure of twin-tub CMOS Inverter

# 3.7.4 Silicon on Insulator (SOI) CMOS Technology

This technology uses sapphire, which is basically an insulator, as the substrate. The advantage of this technology is that problem such as latch-up or body effect is not an issue, hence it can operate at higher speed. However, the process is more expensive, poorer in heat conduction and relatively low in yield.

# 3.7.5 Fabrication of a CMOS Inverter

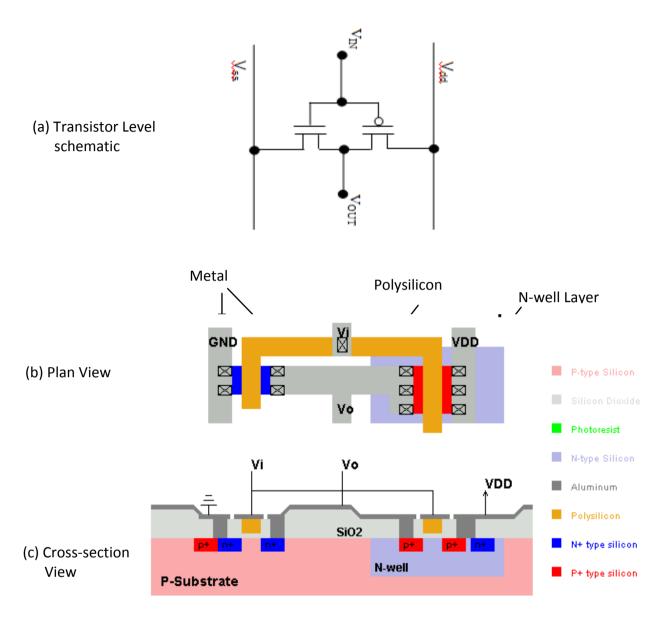

Figure 3-47 shows the layout diagram of a CMOS inverter using NWELL process.

Figure 3-47 Translation of CMOS Inverter To Mask Design

#### Figure 3-48 shows the fabrication sequences of the CMOS inverter.

# **Review Questions**

## Question 1

- (a) From the diagram given in Figure 3-49, identify the :-

- (i) type of the MOS transistor.

- (ii) gate, source and drain terminals.

Figure 3-49 MOS transistor

(b) State the current equation of the MOS transistor under Linear Mode. Based on the current equation, explain the effects of having a long channel length or a wide channel width.

#### Solution to Q1

(a)

An NMOS transistor (Both Source and Drain are of n+ diffusion)

(b) A MOS transistor is in linear mode when  $V_{gs} \ge V_{tn}$  and  $V_{ds} < (V_{gs} - V_{tn})$ . The associated current equation is :-

$$I_{ds} = K_n[W/L][(V_{gs} - V_{tn})V_{ds} - V_{ds}^2/2]$$

→  $I_{ds} \alpha$  (W/L)

Thus, if length (L) increases, I<sub>ds</sub> decreases. if width(W) increases, I<sub>ds</sub> increases.

Explain what does each of the following statement means when referring to a MOS transistor.

- (a) It is a symmetrical device.

- (b) It is a voltage-controlled device.

- (c) It is a unipolar device.

#### Solution to Q2

(a) A MOS transistor is a **symmetrical device** because source and drain terminal are interchangeable. It depends on the voltage potential at the terminal with respect to one another to determine its characteristic.

For NMOS transistor, the source terminal is always at a lower potential than the drain terminal and vice versa for PMOS transistor.

(b) A MOS transistor is a **voltage-controlled device** because a bias voltage needs to be applied to the gate terminal to turn 'ON' or 'OFF' the device.

A gate voltage of  $|V_{gs}| > V_{th}$  is required to turn on transistor. For NMOS transistor,  $V_{th} \approx 0.2V_{dd}$  while for PMOS transistor,  $V_{th} \approx -0.2V_{dd}$ .

(c) A MOS transistor is a **unipolar device** because conduction (current flow) depends only on the majority carriers. For an NMOS transistor, electrons are the majority carriers while for PMOS transistor, holes are the majority carriers.

- (a) Explain the three modes of operations of an NMOS enhancement transistor by :-

- (i) drawing and labelling the various cross sectional structures.

- (ii) providing the voltage conditions and current equations for each mode of operation.

- (b) Sketching the current  $(I_{ds})$  versus voltage  $(V_{ds})$  characteristic curve. Indicate the 3 regions of operation.

#### Solution to Q3

(a) A basic enhancement mode MOSFET does not have a channel established at fabrication thus it is a normally OFF device. The 3 modes of operation are :-

#### Cut-off Mode

When the voltage applied to the gate of the transistor is such that  $V_{gs} < V_{th}$ , where  $V_{th} \approx 0.2V_{dd}$ , no conducting channel is induced resulting in the path resistance between the source and drain being very high and hence  $I_{ds} = 0$ .

NMOS transistor in Cutoff Mode Operation

#### Triode/Linear Mode

When  $V_{gs} \ge V_{th}$  and  $V_{ds} < (V_{gs} - V_{th})$ , electrons (carriers) accumulated near the surface under the gate region starts to gather to create a conducting channel between the source and the drain. With the channel, current can now flow from the drain to the source (opposite to electron flow).

NMOS transistor in Triode/linear Mode

#### Saturation Mode

When  $V_{gs} \geq V_{th}$  and  $V_{ds} \geq (V_{gs} - V_{th})$ , the channel will become tapered, as shown in the figure below, because the effective voltage on the channel decreases towards the drain end. The current  $I_{ds}$  is also affected. The  $I_{ds}$  under this condition is given as :-

NMOS Transistor in Saturation Mode

#### (b) NMOS Current (I<sub>ds</sub>) versus voltage (V<sub>ds</sub>) characteristic curve

NMOS VI Characteristics Curve

For an NMOS enhancement transistor, with V<sub>t</sub> = 0.4V, V<sub>gs</sub> = 1V, L = 0.18µm, W = 5µm, K<sub>n</sub> =  $\mu_n \epsilon_o \epsilon_r / t_{ox} = 100 \mu A/V^2 = 100 \mu F/V$ -sec, calculate:-

(a) its current when  $V_{ds} = 1.0V$ .

(b) its current when  $V_{ds} = 0.5V$ .

#### Solution to Q4

| (a) | <u>V<sub>ds</sub> = 1.0 V</u> |                                                                                                                              |                                     |

|-----|-------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|     | —                             | $V_{gs} - V_t = 1 - 0.4 = 0.6 V$                                                                                             |                                     |

|     | Since                         | $V_{ds} > (V_{gs} - V_{th})$                                                                                                 | ➔ transistor is in Saturation Mode. |

|     | Thus,                         | $I_{ds} = \{K_n/2\}[W/L](V_{gs} - V_{tn})^2$<br>= 100*10 <sup>-6</sup> /2 * (5/0.18) * (0.6) <sup>2</sup><br>= <u>0.5 mA</u> |                                     |

(b)<u>V<sub>ds</sub> = 0.5 V</u>

Since

$V_{gs} - V_{th} = 1 - 0.4 = 0.6 V$

$V_{ds} < (V_{gs} - V_{th})$   $\rightarrow$  transistor is in Triode Mode.

Thus,  $I_{ds} = K_n [W/L] [(V_{gs} - V_{tn})V_{ds} - V_{ds}^2/2]$   $= 100^* 10^{-6} * (5/0.18) * [0.6^* 0.5 - 0.5^2/2]$  = 0.486 mA

Explain with the aid of diagrams why a N-channel (NMOS) pass transistor transfers :-

- (a) logic "High" with degradation.

- (b) logic "Low" without degradation.

## Solution to Q5

**NMOS** Pass Transistor

An NMOS transistor can act like a switch. A signal voltage, S, is applied at the gate (with respect the source terminal;  $V_{gs}$ ) to control the ON and OFF of the transistor. When S is low, the transistor is OFF and when S is high ( $V_{dd}$ ), the transistor is ON.

#### (a) $V_{in}$ = High and $C_{load}$ is initially uncharged

$C_{load}$  will starts to charge when the switch is ON, however  $V_{out}$  can only reach  $V_{in}$ - $V_{tn}$  because exceeding this value, the ON condition will cease to exist and the transistor will turn OFF. Hence, it can be concluded that NMOS transistor *transfers logic High with degradation*. That is, the  $V_{out}$  cannot reach full  $V_{in}$ . The direction of the current flow is from left to right.

#### (b) $V_{in}$ = Low and $C_{load}$ is initially charged to $V_{in}$ - $V_{tn}$

With the switch is closed,  $C_{load}$  will starts to discharge and the current flows from right to left. This action can continues until  $C_{load}$  discharges to 0V. Thus, NMOS transistor *transfers Low logic without degradation*.

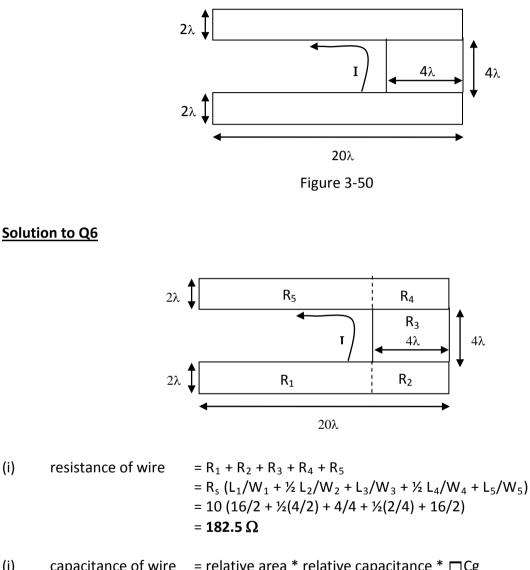

Figure 3-50 shows a polysilicon wire with sheet resistance,  $R_s = 10 \Omega/\Box$ . If the relative capacitance for polysilicon to substrate is 1.0 □Cg, compute the followings :-

- resistance of the polysilicon wire in ohms. (a)

- (b) capacitance of the polysilicon to substrate in terms of  $\Box$ Cg.

(i) capacitance of wire = relative area \* relative capacitance \*

Cg = (A<sub>1</sub> + A<sub>2</sub> + A<sub>3</sub>)/4 \* 1 \* □Cg = (2\*20 + 4\*4 + 2\*20)/4 \* 1 \* □Cg = 96 □Cg

Note: relative area = ratio of actual area (A) to area of a minimum sizes gate

(i)

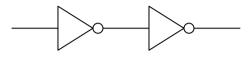

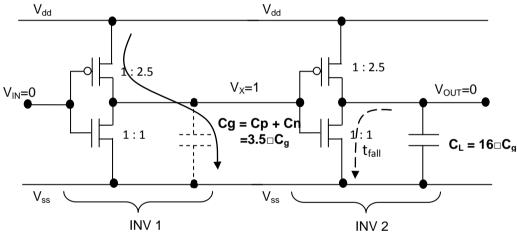

Figure 3-51 shows two CMOS inverters cascaded together to drive a capacitive load of  $C_L = 16 \Box Cg$ . Assume  $W_p = 2.5W_n$ , for  $V_{in} = Low$  and  $V_{in} = High$ , calculate:-

(a) the delay experienced by the pair (from  $V_{in}$  to  $V_{out}$ ) in terms of  $\tau$ .

(b) average propagation delay, t<sub>p</sub>.

Assume minimum-sized transistors for NMOS.

Figure 3-51

#### Solution to Q7

Transistor Level Circuitry

(a)(i) When  $V_{IN} = LOW$

$T_{INV1}(OFF) = R_pC$ = R<sub>SP</sub> (1/2.5)\* 3.5 \[Cg] = (2.5 R\_{SN})(1/2.5) \* 3.5 \[Cg] = 3.5 \[T]

$$T_{INV2}(ON) = R_n C$$

=  $R_{SN} (1/1) * 6 \Box C_g$

=  $16 \tau$

$t_{pHL} = 3.5 \tau + 16 \tau$

=  $19.5 \tau$

## (a)(ii) When V<sub>IN</sub> = HIGH

$$T_{INV1}(ON) = R_nC$$

=  $R_{SN} (1/1)^* 3.5 \Box C_g$

=  $3.5 \tau$

$$T_{INV2}(OFF) = R_pC$$

=  $R_{SP} (1/2.5) * 16 \Box C_g$

=  $(2.5 R_{SN})(1/2.5) * 16 \Box C_g$

=  $16 \tau$

$$t_{pLH} = 3.5 \tau + 16 \tau$$

=  $19.5 \tau$

(b) Average propagation delay =  $(t_{pHL} + t_{pHL})/2$ =  $(19.5 \tau + 19.5 \tau) / 2$ = **19.5 τ**

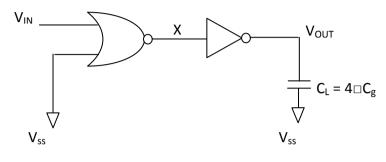

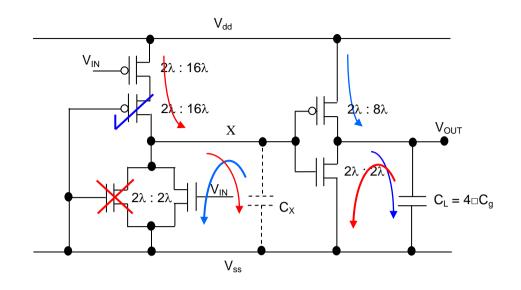

For the CMOS circuit shown in Figure 3-52, the PMOS transistor size of the NOR gate is W=16 $\lambda$ , L=2 $\lambda$  and that of the inverter is W=8 $\lambda$ , L=2 $\lambda$  respectively. The NMOS transistor size in both the inverter and NOR gate is L=2 $\lambda$  and W=2 $\lambda$ .

Figure 3-52

- (a) Draw the transistor level circuitry for the circuit shown.

- (b) Calculate the  $V_{IN}$  to  $V_{OUT}$  delay in terms of  $\tau$  and indicate the direction of current flow if  $V_{IN}$  = High.

- (c) Calculate the  $V_{IN}$  to  $V_{OUT}$  delay in terms of  $\tau$  and indicate the direction of current flow if  $V_{IN}$  = Low.

- (d) If the sizes of the PMOS transistors are the same as those of the NMOS transistors, comment on its effect on symmetricity of timing and performance of the circuit.

## Solution to Q8

(a)

$$C_X = C_p + C_n$$

$= \frac{(2*8)}{(2*2)} \Box C_g + \frac{(2*2)}{(2*2)} \Box C_g$

$= 5 \Box C_g$

where C = rel area \* rel cap \*  $\Box C_g$

(b) When

$$V_{IN} = "H"$$

, time taken to discharge  $V_X$  to "L" is :

$$T_{NOR}(ON) = RC$$

$$= R_{Sn} \left(\frac{2}{2}\right) \times 5 \Box C_g$$

$$= 5 \tau$$

With  $V_X$  = "L", time taken to charge  $V_{\text{OUT}}$  to "H" is :

$$\begin{array}{l} {\sf T}_{\sf INV}({\sf OFF}) \ = {\sf R}_{\sf Sp} \ (\frac{2}{8}) \ x \ 4 \Box {\sf C}_g \\ \\ = 2.5 \ {\sf R}_{\sf Sn} \ (\frac{2}{8}) \ x \ 4 \Box {\sf C}_g \\ \\ = 2.5 \ \tau \end{array} \qquad \mbox{where } {\sf R}_{\sf Sp} \approx 2.5 \ {\sf R}_{\sf Sn} \end{array}$$

Total Delay =  $T_{NOR}(ON) + T_{INV}(OFF)$ = (5 + 2.5)  $\tau$ = **7.5**  $\tau$  (c) When  $V_{IN} = "L"$ , time taken to charge  $V_X$  to "H" is :

$$T_{NOR}(OFF) = RC$$

=  $R_{Sp} \left(\frac{2}{16} + \frac{2}{16}\right) \times 5 \Box C_g$

=  $2.5R_{Sn} \left(\frac{2}{16} + \frac{2}{16}\right) \times 5 \Box C_g$  where  $R_{Sp} \approx 2.5 R_{Sn}$

=  $3.125 \tau$

With  $V_X = "H"$ , time taken to discharge  $V_{OUT}$  to "L" is :

$$T_{INV}(ON) = R_{Sn} \left(\frac{2}{2}\right) \times 4\Box C_g$$

$$= 4 \tau$$

Total Delay =  $T_{NOR}(OFF) + T_{INV}(ON)$ = (3.125 + 4)  $\tau$ = **7.125**  $\tau$

(d) The difference in sizing between the two types of transistors allows a more symmetrical propagation delay to be obtained.

However, if the two sets of transistors are made the same size, then the taken by the NOR gate when  $V_{IN} = "L"$  will be much longer, approx  $25\tau$ , while that taken by the INV when  $V_{IN} = "H"$  will be approx  $10\tau$ . These differences not only affect the symmetricity of the timing but also significantly reduce the performance of the circuit.

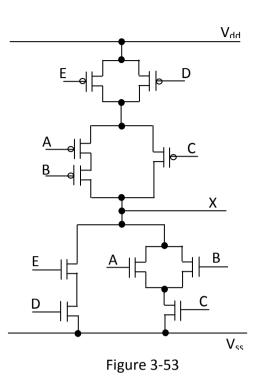

For the circuit shown in Figure 3-53 determine the boolean expression at X.

### Solution to Q9

X = DE + C(A+B)

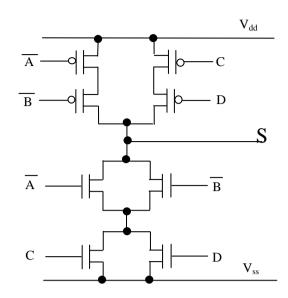

- (a) Show the CMOS transistor level implementation of  $S = \overline{A.B.}(C + D)$  using:

- (i) three 2-inputs NAND gates only.

- (ii) complex gate concept.

Assume the *negated* signals are readily available.

- (b) With reference to part(a), which implementation is the preferred choice. Why?

- (c) With reference to a 3-inputs NAND gate, if the p-transistors and n-transistors are of the same size, will the rise time be shorter than, longer than or equal to the fall time? Why?

- (d) Explain briefly why CMOS circuitry is known to be ratioless.

- (e) Discuss briefly the power dissipation in CMOS circuitry.

#### Solution to Q10

(a) (i)  $S = A \cdot B \cdot (\overline{C} \cdot \overline{D})$

Function Implemented Using Standard NAND Gates Concept

(ii)

$$S = (\overline{A} + \overline{B}) \cdot (C + D)$$

Function Implemented Using Complex Gates Concepts

- (b) The Complex Gates implementation is preferred as it requires fewer transistors for implementation of the same function.

- (c) As electrons has a mobility of about  $2.5x \sim 3x$  that of holes, for transistors of equal sizes,  $R_p \approx 3R_n$ .

During  $T_{ON}$ , all 3 n-transistors will be ON, hence the total resistance experienced during this time is  $3R_n$ . Thus,  $T_{fall} \approx 3 R_n C$ .

For T<sub>OFF</sub>, 3 possibilities exist namely:

- 1 PMOS is ON:- the total resistance experienced during this time is  $R_p$  ( $\approx 3R_n$ ). Thus,  $T_{rise} \approx 3R_nC$ .

- 2 PMOS are ON: the total resistance experienced during this time is  $\frac{1}{2}R_p$  ( $\approx 1.5R_n$ ). Thus,  $T_{rise} \approx 1.5R_nC$ .

- 3 PMOS are ON: the total resistance experienced during this time is  $1/3 R_p$  ( $\approx R_n$ ). Thus,  $T_{rise} \approx R_n C$ .

Hence, the  $T_{rise}$  is generally shorter than the  $T_{fall}$  except under worst case scenario. The shorter  $T_{rise}$  is due to the parallel combination of the PMOS.

- (d) CMOS circuits are ratioless because  $V_{OL} = V_{ss}$  (ground) and does not depends on the ratio of PMOS to NMOS transistors.

- (e) At  $V_{OL}$ , only NMOS is 'ON' while PMOS is 'OFF' and vice versa when output is at  $V_{OH}$ . Hence, no current flows from  $V_{dd}$  rail to  $V_{ss}$  rail.

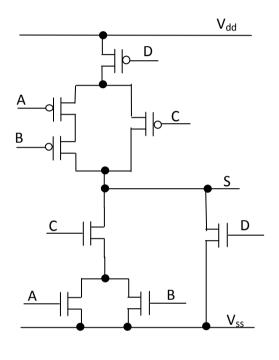

Given the following Boolean equations, show their implementation using complex gate concept in CMOS technology.

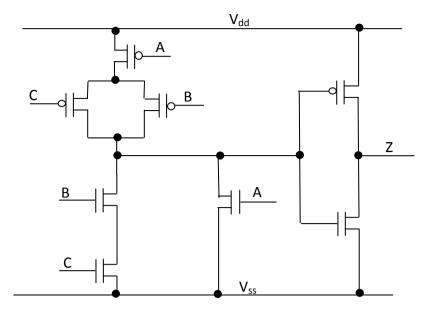

(a) X = (A + B) C + D

(b)

$$Y = A + D (B + \overline{C})$$

#### Solution to Q11

(b)

$$Y = A + D (B + C)$$

(c) Z = A + B C

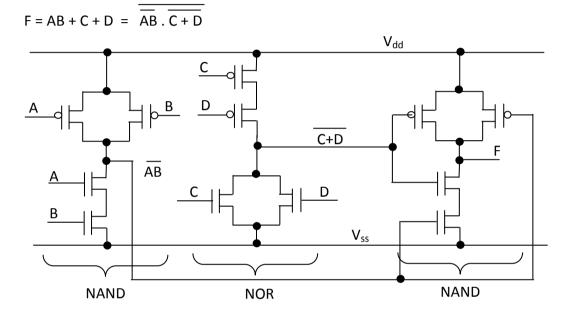

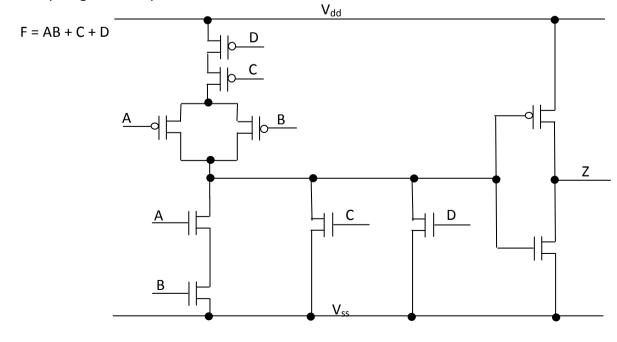

For the logic function F = AB + C + D, show how it can be implemented in CMOS technology using:

- (a) standard NAND/NOR/INVERTER gates.

- (b) complex gate concept.

### Solution to Q12

(a) standard NAND/NOR/INVERTER gates.

(b) Complex gate concept

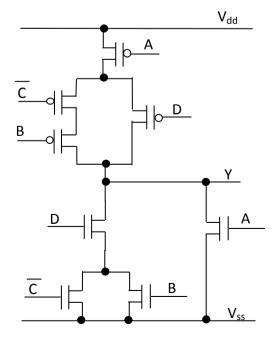

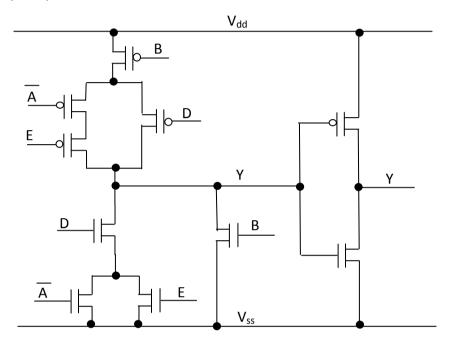

For the logic function  $X = B + D (E + \overline{A})$ ,

- (a) show its implementation using CMOS complex gate.

- (b) indicate and explain which transistors in the circuit is affected by body effect.

#### Solution to Q13

(a)  $Y = B + D(E + \overline{A})$

(b) When two devices are connected is series (e.g. NAND gate), their  $V_{sb}$  will be different, that is,  $V_{sb1} = 0$  but  $V_{sb2} \neq 0$ . With  $V_{sb2} \neq 0$ , an increase in the thickness of the depletion region under the channel of will occur. The increased depletion layer requires additional charge to be supplied. If  $V_{gs}$  is held constant, the charge in the channel will decrease thereby reducing conductivity. To maintain the channel conductivity,  $V_{gs}$  need to increase.

Thus, transistors whose  $V_{sb2} \neq 0$  are said to experience body effect.

Transistors experiencing body effect are : NMOS - D

PMOS - A, E, D

(a) Determine the boolean expression at X.

(b) Redraw using CMOS dynamic gate concept.

## Solution to Q14

(a)

$$X = \overline{\overline{DE} + B}$$

(b)

- (a) Sketch the cross-sectional structure of a N-well process CMOS inverter showing all parasitic elements that constitute the occurrence of latch-up.

- (b) Explain how latch-up occurs and how can it be overcome.

#### Solution to Q15

(a)

(b) Latch up is the inadvertent creation of a low-impedance path between the power supply rails of a CMOS circuit. It occurs when the parasitic structure within the CMOS circuit is activated thus disrupting proper functioning of the part and possibly even leading to circuit destruction due to over-current.

A scenario of latch-up is when sufficient current flows through  $R_{sub}$ , which in turn causes  $Q_2$  to turn ON. With  $Q_2$  ON, current will be drawn through  $R_{well}$ . If sufficient voltage develops across  $R_{well}$ ,  $Q_1$  can then turn ON, causing more current to flow throug

$R_{sub}$  is due to the p-substrate  $R_{well}$  is due to the n-well

Latch up in CMOS circuits can be reduced by :-

- (i) increasing the distance between N-well and N+ source/drain diffusion of the NMOS device  $\Rightarrow$  reduction of  $\beta_2$ .

- (ii) using guard rings around the transistors to provide a low resistance path to collect holes before they interfere with the operation of other circuits outside the guard ring.

- (iii) placing a well tie and a substrate tie close to the supplies. These will in turn reduce the value of  $R_{sub}$  and  $R_{well} \Rightarrow$  higher accidental current is required to cause latch-up.

- (iv) increase substrate doping level  $\Rightarrow$  reduction in  $R_{sub}$

## Chapter 3 – Summary

## 3.1.4 Operation of NMOS Enhancement Transistor

Source (S)  $\leftarrow \rightarrow$  Drain (D) Source is the terminal with a *lower* voltage (V<sub>s</sub> < V<sub>D</sub>)

## 3 modes of Operation

## **3.1.4** Operation of PMOS Enhancement Transistor

## **3** modes of Operation

# Summary of Operation Modes

|                                                   | Pg 7 NMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pg 7 PMOS                                                                                                                                                                                  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFF                                               | $V_{gs} < V_t$ where $V_t \approx 0.2V_{dd}$ and $V_{dd} = 1.2V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{gs} > V_t$ where $V_t \approx -0.2V_{dd}$ and $V_{dd} = 1.2V$                                                                                                                          |

| ON :                                              | $V_{gs} \ge V_t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{gs} \leq V_t$                                                                                                                                                                          |

| Linear Region                                     | $V_{ds} < (V_{gs} - V_t)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{ds} > (V_{gs} - V_t)$                                                                                                                                                                  |

|                                                   | $I_{ds} = K_n [W/L] [(V_{gs} - V_t)V_{ds} - V_{ds}^2/2]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $I_{ds} = K_p[W/L][(V_{gs} - V_t)V_{ds} - V_{ds}^2/2]$                                                                                                                                     |

| ON :                                              | $V_{gs} \ge V_t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $V_{gs} \leq V_t$                                                                                                                                                                          |