# How to kickstart App Development using Xilinx Ultrascale+ RFSoC ZCU216 Eval Platform

1

seeteck@gmail.com

# **Content:**

Skillset needed

Xilinx RFSoC

Tools & Reference Designs

Brief Intro to Reference Design

Demo: Vivado and Vitis Project Directory

Slide + Demon (if time allowed) will take about 50 min

# **Skillset - Roughly 5 Categories:**

Architecture (FPGA, Prototype Platform)

HDL (hardware description language)

FPGA Design Flow (Integration of IP, Simulation, Synthesis, Implementation, Verification)

Embedded C

Compiler and IDE (Tool Chain)

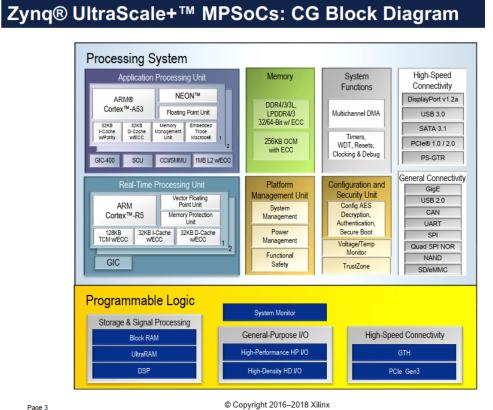

### Architecture of FPGA

RESoC = MPSoC + Data Converters

- Basic understanding of Processing System such as CPU, APU, RPU, MMU, Cache, DMA, DDR and etc.

- Basic understanding of commonly used connectivity such as UART, USB, I2C, SPI, ethernet and etc.

- Understanding of resources of Programmable Logic such as BRAM, URAM, DSP, GPIO, LUT, SLICE, CLB, IO standard and etc.

- Understanding of IP blocks such as FFT, FIR, DDS, NCO, PLL, Memory Controller and etc.

### HDL

• Either VHDL or SystemVerilog

```

34 🗄

--down counter

--when enable, count from max count to min count

36

--assert count end when min count reach

procedure time counter (signal en

: in std logic;

signal max count

: in unsigned (31 DOWNTO 0);

variable count

39

: inout unsigned (31 DOWNTO 0);

40

constant min count

: in unsigned (31 DOWNTO 0);

41

signal count end

: out std logic) is

42

begin

43

if en = '1' then

44

count := count - 1:

45 🛱

if count = min count then

46

count end <= '1';

47

end if;

48

else

49

count := max count;

count end <= '0';

end if;

end time counter;

54

begin

--- control duration of toff

p toff: process(clk)

59

variable t : unsigned(31 DOWNTO 0);

60

begin

61

if rising_edge(clk) then

62

time counter (en toff, t off, t, TO UNSIGNED (2,32), toff stop);

63

end if;

64

count toff <= t;

65

end process;

```

- Able to write/read with 1 language (writing is always difficult than reading)

Able to read with another language.

- Sometimes you need to understand, adapt and modify code that is written in another language

- Different level of mastery of language will impact design quality, upgradability and maintainability of code

- Undetected bug could be as simple as harmless and no body will ever detect it or disaster waiting to be happen

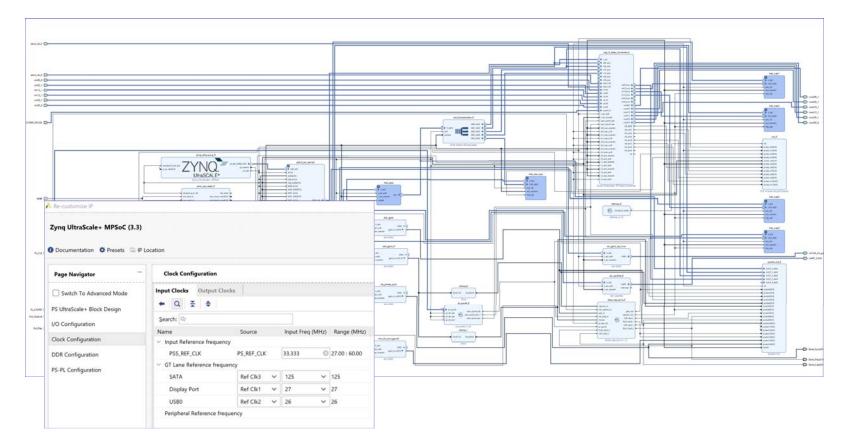

### **Design Flow – IP Integration**

- □ Able to configure each IP Core and Connect them together

- □ IP-reuse is essential part of fpga design

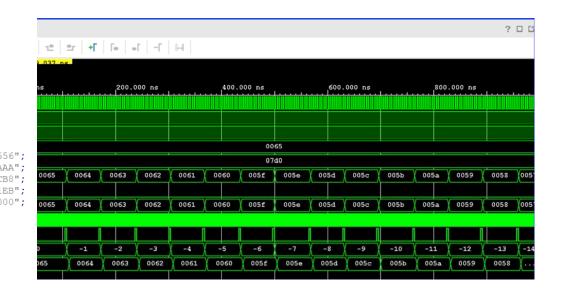

### **Design Flow – Simulation**

```

16

entity tb chirp is

17

end tb chirp;

19

architecture behave of the chirp is

20

COMPONENT chirp dds

PORT (

23

aclk : IN STD LOGIC;

24

aclken : IN STD LOGIC;

25

aresetn : IN STD LOGIC;

26

s axis phase tvalid : IN STD LOGIC;

27

s axis phase tdata : IN STD LOGIC VECTOR (71 DOWNTO 0);

28

m axis data tvalid : OUT STD LOGIC;

29

m axis data tdata : OUT STD LOGIC VECTOR (31 DOWNTO 0);

m axis phase tvalid : OUT STD LOGIC;

m axis phase tdata : OUT STD LOGIC VECTOR (31 DOWNTO 0)

);

END COMPONENT;

34

signal clk

: std logic;

36

signal en, en1, op_start, op_stop

: std logic;

-- -10M to +10M, Ton=2us

constant freq start

: STD LOGIC VECTOR (31 DOWNTO 0) := X"F5955556";

40

constant freq stop

: STD LOGIC VECTOR (31 DOWNTO 0) := X"0A6AAAAA";

41

constant freq step

: STD LOGIC VECTOR (31 DOWNTO 0) := X"000ADCB8";

: STD LOGIC VECTOR (31 DOWNTO 0) := X"000001EB";

42

constant time on

43

constant time off

: STD LOGIC VECTOR (31 DOWNTO 0) := X"00000000";

44

45

signal cos, sin

: STD LOGIC VECTOR (11 DOWNTO 0);

46

signal wf cos, wf sin : STD LOGIC VECTOR (11 DOWNTO 0);

47

signal phase out

: STD LOGIC VECTOR (31 DOWNTO 0);

48

signal dum0, dum1

: STD LOGIC VECTOR (3 DOWNTO 0);

49

signal dum2

: STD LOGIC VECTOR (6 DOWNTO 0);

```

Able to write good test bench to fully verify design, especially when designer and verifier are the same person

7

### **Design Flow – Verification (timing-closure)**

- Concept of STA (static timing analysis), setup & hold time of digital circuit, clock domain, metastability and etc.

- Able to write the necessary constraint and false-path if necessary, in order to close timing

Familiar with tcl language (google

- "ug835" and "ug894"

### Q | 🖬 | ← | ≁ | X | 🖻 | 🗈 | X | // | 🎟 | ♀ |

```

#We need this PL CLK to latch in PL SYSREF, then cross into ADC or DAC stream clock

1

#Our stream clock source from RFDC-PLL output, not from PL CLK (external from PCB)

2

#Take out, MMCM input is def by tools

3

create clock -period 8.138 -name pl clk in [get ports FPGA REFCLK OUT C P]

4

5

6

#External PL clk (122.88MHz) go into MMCM to produce 491.52MHz for baseband clk

create_generated_clock -source [get_ports FPGA REFCLK OUT C P] -divide by 1 [get_pins i mmcm pl/inst/clk in1]

7

8

#$clk pl 0 (named by tools) is clk from ps8. 100MHz not related to baseband clock

9

set clock groups -name async ps mmcm -asynchronous -group [get clocks -of objects [get pins {i ps/ps block i/zynq ultra ]

10

11

#up bus timing

12 '

set false path -from [get pins -of [get cells -hier -filter {NAME =~ "*i reg*e1 reg"}] -filter REF PIN NAME==C] -to [get

13

set_max_delay -datapath only -from [get_clocks [get_clocks -of objects [get_pins {i ps/ps block i/zynq ultra ps e 0/U0/P

14

15 set max delay -datapath only -from [get clocks [get clocks -of objects [get pins {i ps/ps block i/zynq ultra ps e 0/U0/P

```

### **Design Flow – Synthesis**

| ttings                |                        |                                  |     |  |  |  |  |

|-----------------------|------------------------|----------------------------------|-----|--|--|--|--|

| Write Incremental S   | Synthesis              |                                  |     |  |  |  |  |

| ncremental synthesis: | tal synthesis: Not set |                                  |     |  |  |  |  |

| Strategy:             | 🔓 Vivado Synthesis     | Defaults (Vivado Synthesis 2019) | ✓ 💾 |  |  |  |  |

| Description:          | Vivado Svnthesis Def   | Vivado Synthesis Defaults        |     |  |  |  |  |

| ∼Synth Design (vivad  |                        |                                  |     |  |  |  |  |

| tcl.pre               |                        |                                  |     |  |  |  |  |

| tcl.post              |                        |                                  |     |  |  |  |  |

| -flatten_hierarchy    |                        | rebuilt                          | ~   |  |  |  |  |

| -gated_clock_conv     | ersion                 | off                              | ~   |  |  |  |  |

| -bufg                 |                        | 12                               |     |  |  |  |  |

| -fanout_limit         |                        | 10,000                           |     |  |  |  |  |

| -directive            |                        | Default                          | ~   |  |  |  |  |

| -retiming             |                        |                                  |     |  |  |  |  |

| -fsm_extraction       |                        | auto                             | ~   |  |  |  |  |

| -keep_equivalent_i    | registers              |                                  |     |  |  |  |  |

| -resource_sharing     |                        | auto                             | ~   |  |  |  |  |

| -control_set_opt_th   | nreshold               | auto                             | ~   |  |  |  |  |

| -no_lc                |                        |                                  |     |  |  |  |  |

| -no_srlextract        |                        |                                  |     |  |  |  |  |

| -shreg_min_size       |                        | 3                                |     |  |  |  |  |

| -max_bram             |                        | -1                               |     |  |  |  |  |

| -max_uram             |                        | -1                               |     |  |  |  |  |

| -max_dsp              |                        | -1                               |     |  |  |  |  |

| -max_bram_cascad      |                        | -1                               |     |  |  |  |  |

| -max_uram_cascad      | le_height              | -1                               |     |  |  |  |  |

| -cascade_dsp          |                        | auto                             | ~   |  |  |  |  |

| -assert               |                        |                                  |     |  |  |  |  |

- Understand how the tool perform mapping between RTL construct and FPGA resource

- Familiar with various attributes or directives (google "ug901")

UNCLASSIFIED

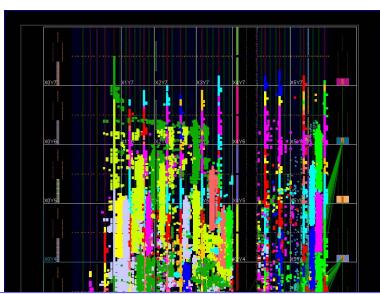

### **Design Flow – Implementation (place and route)**

- Understand the quality of the implemented design, such as resource usage, power consumption and etc

- Familiar with various attributes and directives (google "ug904") and how to apply them if implementation can't pass timing

| Name       | Slack ^ 1 | Levels | High Fanout | From                                | То                                              | Skew   | Total Delay | Logic Delay | Net Delay | Logic % | Net % | Requirement | Source Clock  |

|------------|-----------|--------|-------------|-------------------------------------|-------------------------------------------------|--------|-------------|-------------|-----------|---------|-------|-------------|---------------|

| 👍 Path 119 | -0.227    | 1      | 145         | g_ch[3].i_ch/i_L2/en0_reg/C         | g_ch[3].i_ch/i_L2/i_filter/conf_valid_q_reg/S   | -0.263 | 1.746       | 0.178       | 1.568     | 10.2    | 89.8  | 2.034       | pl_clk_491p52 |

| 🤸 Path 120 | -0.221    | 1      | 145         | g_ch[3].i_ch/i_L2/en0_reg/C         | g_ch[3].i_ch/i_L2/i_filter/conf_valid_i_reg/S   | -0.317 | 1.686       | 0.178       | 1.508     | 10.6    | 89.4  | 2.034       | pl_clk_491p52 |

| Ъ Path 121 | -0.214    | 1      | 145         | g_ch[3].i_ch/i_L2/en0_reg/C         | g_ch[3].i_ch/i_L2/i_filter/conf_data_reg[0]/CE  | -0.318 | 1.691       | 0.178       | 1.513     | 10.5    | 89.5  | 2.034       | pl_clk_491p52 |

| Ъ Path 122 | -0.063    | 4      | 3           | g_ch[1].i_ch/i_L2/data_del_reg[5]/C | g_ch[1].i_ch/i_L2/i_delay/adr_out_bot_reg/D     | -0.385 | 1.559       | 0.474       | 1.085     | 30.4    | 69.6  | 2.034       | pl_clk_491p52 |

| Ъ Path 123 | -0.047    | 1      | 2           | tor.decimation_filter/DOUT_reg[3]/C | iftreg.gen_rtl_delay.delay_bus_reg[3][3]_srl4/D | -0.373 | 1.470       | 0.220       | 1.250     | 15.0    | 85.0  | 2.034       | pl_clk_491p52 |

| Ъ Path 124 | -0.044    | 3      | 3           | g_ch[7].i_ch/i_L1/data_del_reg[3]/C | g_ch[7].i_ch/i_L1/i_delay/adr_out_sub_reg[15]/D | -0.333 | 1.592       | 0.433       | 1.159     | 27.2    | 72.8  | 2.034       | pl_clk_491p52 |

|            |           |        |             |                                     |                                                 |        |             |             |           |         |       |             |               |

### **Embedded C**

```

70⊖err t recv callback(void *arg, struct tcp pcb *tpcb,

71

struct pbuf *p, err_t err)

72 {

/* do not read the packet if we are not in ESTABLISHED state */

73

74

if (!p) {

75

tcp_close(tpcb);

76

tcp_recv(tpcb, NULL);

77

return ERR_OK;

78

}

79

80

/* indicate that the packet has been received */

81

tcp_recved(tpcb, p->len);

82

83

ip len = p->len;

//xil_printf("p->len = %d \n\r", p->len);

84

85

memcpy((void*)ip buf, p->payload, ip len);

86

ip ptr = (char*) p->payload;

87

*(ip buf + ip len) = 0; //terminate string for app buffer

88

//xil_printf("lwip pter %p, app pter %p\n\r", ip_buf, ip_ptr);

89

gps flag ip = 1;

90

/* echo back the payload */

91

92

/* in this case, we assume that the payload is < TCP SND BUF */

93

if (tcp sndbuf(tpcb) > p->len) {

err = tcp write(tpcb, p->payload, 1, 1); //echo 1st byte as ACK

94

95

} else

96

xil_printf("no space in tcp_sndbuf\n\r");

97

98

/* free the received pbuf */

99

pbuf_free(p);

```

- Familiar with embedded C from basic to more advanced pointer

- Have basic concept of polling and interrupt service routine

- Able to use API or driver provided by BSP

### **Compiler and Toolchain**

□ Familiar with IDE such as Eclipse, Vitis or etc, and proper organization of C code and header files.

| <ul> <li>ggs_app [ standalone on psu_cortexa</li> <li>Binaries</li> </ul>                                                                                                                                                                                                                  | 5 ^ type filter text                                                                                                                                                                 | Board Support Package                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| > 🔊 Includes<br>> 🗁 Debug<br>Y 🧀 src                                                                                                                                                                                                                                                       | <ul> <li>✓ □ psu_cortexa53_0</li> <li>✓ □ zynqmp_fsbl</li> </ul>                                                                                                                     | View current BSP settings, or configure settings li<br>change versions of OS/libraries/drivers etc.                                                                                                                                                                                                                                                                                                             |

| <ul> <li>console_commands</li> <li>c cli.c</li> <li>h cli.h</li> <li>c echo.c</li> <li>c gps_function.c</li> <li>h gps_function.h</li> <li>c gps_tcp.c</li> <li>h gps_tcp.h</li> <li>c LMK_display.c</li> <li>h LMK_display.c</li> <li>h LMK_display.c</li> <li>h LMK_display.c</li> </ul> | <ul> <li>Board Support Package</li> <li>standalone on psu_cortexa53_0</li> <li>Board Support Package</li> <li>psu_pmu_0</li> <li>psu_pmufw</li> <li>Board Support Package</li> </ul> | Modify BSP Settings       Reset BSP Sources         A BSP settings file is generated with the user opti modifications done. All the subsquent changes ar Load BSP settings from file         Operating System         Name:       standalone         Version:       7.5         Description:       Standalone is a simple, low-lev basic features of a hosted envi         Documentation:       standalone v7.5 |

| <ul> <li>imain.c</li> <li>imain.h</li> <li>implatform_config.h</li> <li>implatform_zynqmp.c</li> <li>implatform.c</li> <li>implatform.h</li> <li>implatform.h</li> </ul>                                                                                                                   | ~                                                                                                                                                                                    | Drivers         Libraries           Name         Driver           axi_bram_ctrl_0         bram           axi_gpio_0         gpio           axi_gpio_spi_mux         gpio                                                                                                                                                                                                                                        |

- Familiar with C library and BSP provided by IP vendors

- Process knowledge about how CPU execute its instruction

- Understand the process of linking and compilation

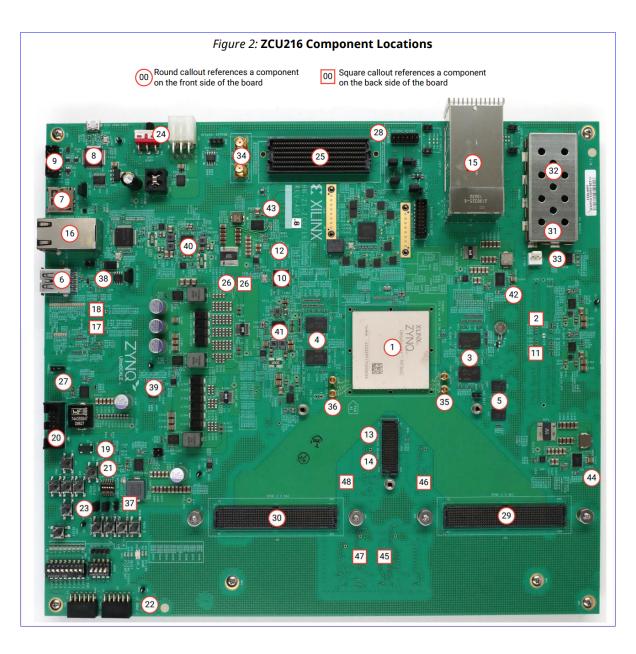

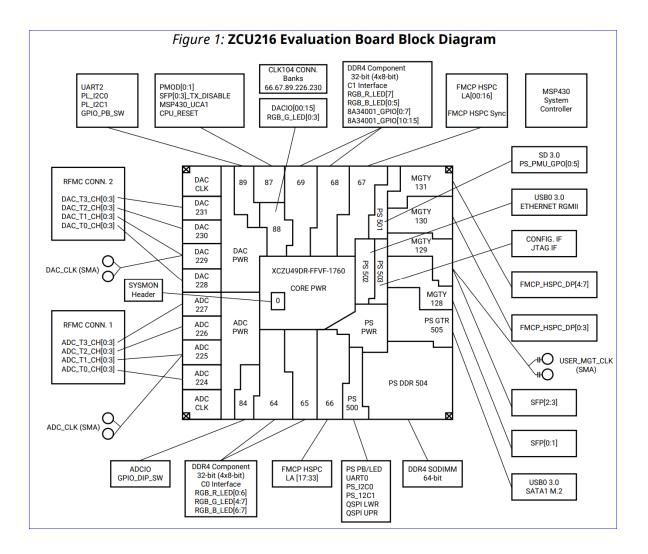

### Zynq UltraScale+ RFSoC ZCU216 Eval Platform

### **TARGET APPLICATIONS**

- > 4G and 5G Remote Wireless Infrastructure

- > Remote Radio for Massive MIMO

- > Fixed Wireless Access

- > 5G Baseband

- > Mobile Backhaul

- > Phased Array Radar

- > Remote-PHY for Cable Access DOCSIS 3.1

- > Test and Measurement

- > Satellite Communications

- > Lidar

- Ug1390

- **Schematic**

- xilinx-rfsoc-product-brief.pdf

### Zynq UltraScale+ RFSoC Feature Summary

#### URAM 80 block of 4K\*72b (288Kb) 80\*4K\*72b = 320K\*72b=23040Kb = = 22.5Mb

#### Table 2: Zynq UltraScale+ RFSoC Feature Summary

|                       |                    | XCZU21DR      | XCZU25DR       | XCZU27DR         | XCZU28DR         | XCZU29DR          | XCZU39DR        | XCZU42DR         | XCZU43DR       | XCZU46DR       | XCZU47DR | XCZU48DR | XCZU49DR |

|-----------------------|--------------------|---------------|----------------|------------------|------------------|-------------------|-----------------|------------------|----------------|----------------|----------|----------|----------|

| 12-bit                | # of ADCs          | 0             | 8              | 8                | 8                | 16                | 16              | -                | -              | -              | -        | -        | -        |

| RF-ADC<br>w/ DDC      | Max Rate<br>(GSPS) | 0             | 4.096          | 4.096            | 4.096            | 2.058             | 2.220           | -                | -              | -              | -        | -        | -        |

| 14-bit                | # of ADCs          | -             | -              | -                | -                | -                 | -               | 8 2              | 4              | 8 4            | 8        | 8        | 16       |

| RF-ADC<br>w/ DDC      | Max Rate<br>(GSPS) | -             | -              | -                | -                | -                 | -               | 2.5 5.0          | 5.0            | 2.5 5.0        | 5.0      | 5.0      | 2.5      |

| 14-bit                | # of DACs          | 0             | 8              | 8                | 8                | 16                | 16              | 8                | 4              | 12             | 8        | 8        | 16       |

| RF-DAC<br>w/ DUC      | Max Rate<br>(GSPS) | 0             | 6.554          | 6.554            | 6.554            | 6.554             | 6.554           | 10.0             | 10.0           | 10.0           | 10.0     | 10.0     | 10.0     |

| SD-FEC                | 1                  | 8             | 0              | 0                | 8                | 0                 | 0               | 0                | 0              | 8              | 0        | 8        | 0        |

| Applicatio<br>Unit    | on Processing      | Quad-core Arr | n Cortex-A53 M | IPCore with Cor  | reSight™; NEO    | N and Single/D    | ouble Precisior | n Floating Point | ; 32KB/32KB L1 | L Cache, 1MB I | 2 Cache  |          |          |

| Real-Time<br>Unit     | e Processing       | Dual-core Arm | Cortex-R5F wi  | ith CoreSight; § | Single/Double P  | Precision Floatin | ng Point; 32KB, | /32KB L1 Cach    | e, and TCM     |                |          |          |          |

| Embedde<br>External   |                    | 256KB On-Chi  | p Memory w/E   | CC; External DI  | DR4; DDR3; DD    | DR3L; LPDDR4;     | LPDDR3; Exte    | ernal Quad-SPI;  | ; NAND; eMMC   |                |          |          |          |

| General (             | Connectivity       | 214 PS I/O; U | ART; CAN; USB  | 2.0; I2C; SPI;   | 32b GPIO; Re     | al Time Clock;    | Watchdog Time   | ers; Triple Time | er Counters    |                |          |          |          |

| High-Spe<br>Connectiv |                    | 4 PS-GTR; PC  | Ie® Gen1/2; S  | erial ATA 3.1; C | )isplayPort 1.2a | a; USB 3.0; SG    | MII             |                  |                |                |          |          |          |

| System L              | ogic Cells         | 930,300       | 678,318        | 930,300          | 930,300          | 930,300           | 930,300         | 489,300          | 930,300        | 930,300        | 930,300  | 930,300  | 930,300  |

| CLB Flip-             | Flops              | 850,560       | 620,176        | 850,560          | 850,560          | 850,560           | 850,560         | 447,360          | 850,560        | 850,560        | 850,560  | 850,560  | 850,560  |

| CLB LUTs              |                    | 425,280       | 310,088        | 425,280          | 425,280          | 425,280           | 425,280         | 223,680          | 425,280        | 425,280        | 425,280  | 425,280  | 425,280  |

| Distribute            | ed RAM (Mb)        | 13.0          | 9.6            | 13.0             | 13.0             | 13.0              | 13.0            | 6.8              | 13.0           | 13.0           | 13.0     | 13.0     | 13.0     |

| Block RA              | M Blocks           | 1,080         | 792            | 1,080            | 1,080            | 1,080             | 1,080           | 648              | 1,080          | 1,080          | 1,080    | 1,080    | 1,080    |

| Block RA              | M (Mb)             | 38.0          | 27.8           | 38.0             | 38.0             | 38.0              | 38.0            | 22.8             | 38.0           | 38.0           | 38.0     | 38.0     | 38.0     |

| UltraRAM              | Blocks             | 80            | 48             | 80               | 80               | 80                | 80              | 160              | 80             | 80             | 80       | 80       | 80       |

| UltraRAM              | (Mb)               | 22.5          | 13.5           | 22.5             | 22.5             | 22.5              | 22.5            | 45.0             | 22.5           | 22.5           | 22.5     | 22.5     | 22.5     |

| DSP Slice             | es                 | 4,272         | 3,145          | 4,272            | 4,272            | 4,272             | 4,272           | 1,872            | 4,272          | 4,272          | 4,272    | 4,272    | 4,272    |

| CMTs                  |                    | 8             | 6              | 8                | 8                | 8                 | 8               | 5                | 8              | 8              | 8        | 8        | 8        |

| Maximum               | n HP I/O           | 208           | 299            | 299              | 299              | 312               | 312             | 128              | 299            | 312            | 299      | 299      | 312      |

| Maximum               | n HD I/O           | 72            | 48             | 48               | 48               | 96                | 96              | 24               | 48             | 48             | 48       | 48       | 96       |

# **Tools:**

### Get the right version

| Xilinx Unified 2021.1 Installer - Vitis Unified Software Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      | _          |          | $\times$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|----------|----------|

| Vitis Unified Software Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>.</b>             | XI         |          | JX.      |

| Customize your installation by (de)selecting items in the tree below. Moving cursor over selections below provide additional information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |            | _        |          |

| The Vitis unified software platform enables the development of embedded software and accelerated applications on heterogeneous Xilinx platfi<br>ACAPs. It provides a unified programming model for accelerating Edge, Cloud, and Hybrid computing applications. This installation is a superse<br>well. Users can add Vitis Model Composer which is a Xilinx toolbox for MATLAB and Simulink to design for AI Engines and Programmable Logic<br>Generator for DSP, you can continue development using Vitis Model Composer.                                                                                                                                                                                                                                            | et that includes the | e Vivado D | esign Su | uite as  |

| Design Tools         Vits Unified Software Platform         Vits         Votade         Votade         Vits         Votade         Devices         Install devices for Alveo and Xilinx edge acceleration platforms         Devices         Socs         Versi         Versi         Versi         Versi         Versi         Versi         Versi         Versi         Devices         Figure ring         Versi         Devices         Tengineering Sample Devices for Custom Platforms         Versi         Install Cable Drivers (You MUST disconnect all Xilinx Platform Cable USB II cables before proceeding) |                      |            |          |          |

| Download Size: NA<br>Disk Space Required: 119.46 GB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | [                    | Resett     | o Defaul | lts      |

| Copyright © 1986-2022 Xilinx, Inc. All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | < Back               | Next >     | С        | Cancel   |

### **Reference Design**

### https://www.xilinx.com/member/zuplus\_rfsoc\_starter\_designs.html

| Zynq UltraScalePlus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RFSoC Starter Designs Site                                                                                                                                                                                                                                                                       |                                                                                                                                                         |                                                                                                                              |                                                                        |                                                            |                                                                            |         |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------|---------|--|

| 脅 / Zynq UltraScalePlus RFSoC Starter Designs Site                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                         |                                                                                                                              |                                                                        |                                                            |                                                                            |         |  |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Documents                                                                                                                                                                                                                                                                                        |                                                                                                                                                         |                                                                                                                              |                                                                        |                                                            |                                                                            |         |  |

| Zynq® UltraScale+™                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RFSoC Starter Designs Secur                                                                                                                                                                                                                                                                      | e Site                                                                                                                                                  |                                                                                                                              |                                                                        |                                                            |                                                                            |         |  |

| Thank you for joining the Zynq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UltraScalePlus RFSoC Starter Designs Secur                                                                                                                                                                                                                                                       | e Site. Here you will find example                                                                                                                      | starter designs for RFSoC.<br>بر                                                                                             | . This information i                                                   | is preliminary an                                          | d subject to change.                                                       |         |  |

| NOTICE: This collection of pre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Idience Please direct any questions regardin<br>release example designs and documentatio                                                                                                                                                                                                         | n are proprietary information of X                                                                                                                      | ilinx, Inc. and is being discl                                                                                               |                                                                        |                                                            |                                                                            | You     |  |

| may use the documentation and examples for evaluation purposes. You may modify example designs for evaluation purposes. The documentation and example designs are provided "as is"<br>without guarantee of Xilinx support. The document collection contains preliminary information and is subject to change without notice. Documents provided herein may relate to products and/or<br>services not yet available for sale, and provided solely for information purposes and are not intended, or to be construed, as an offer for sale or an attempted commercialization of such products<br>and/or services. |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                         |                                                                                                                              |                                                                        |                                                            |                                                                            |         |  |

| Export Administration Regulation<br>reexported, or transferred (in-co<br>local trade regulations. With res<br>technical data on the Commerc                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R: The Materials may contain technical data<br>ons ("EAR") administered by the U.S. Departr<br>puntry) to any other person or company with<br>spect to any controlled technical data you re<br>ce Control List of the EAR, but you are solely<br>quired in order for you to export, reexport, or | ment of Commerce's Bureau of Ind<br>out first obtaining an export licens<br>ceive from Xilinx, Xilinx will provid<br>responsible for the classification | dustry and Security and loca<br>se or other approval that ma<br>e reasonable assistance to<br>per any local trade regulation | cal trade regulations<br>hay be required under<br>by you in connection | s. The Materials<br>er applicable pro<br>with the classifi | may not be exported,<br>ovisions of the EAR and<br>cation of any controlle | d<br>ed |  |

### Zynq® UltraScale+™ RFSoC Starter Design Documents & Files

Here you will find preliminary documentation on Zynq UltraScalePlus RFSoC Starter Designs.

#### Documents

|  | Description | Design <b>Link</b> | Rev | Board | Tool<br>Version | DAC<br>(GSPS) | ADC<br>(GSPS) | Real<br>or<br>IQ | MTS | Software |

|--|-------------|--------------------|-----|-------|-----------------|---------------|---------------|------------------|-----|----------|

|--|-------------|--------------------|-----|-------|-----------------|---------------|---------------|------------------|-----|----------|

| 9  | ZCU111 DMA<br>Play Capture<br>2019.2.1                     | zcu111_dma_2019.2.1_RevA.zip       | А | ZCU111 | 2019.2.1 | 1.47456 | 1.47456 | Real | No  | Bare-<br>Metal |

|----|------------------------------------------------------------|------------------------------------|---|--------|----------|---------|---------|------|-----|----------------|

| 10 | ZCU111 PL<br>DDR4 Play and<br>Capture with<br>DMA 2019.2.1 | zcu111_dma_MIG_2019.2.1_RevA.zip   | A | ZCU111 | 2019.2.1 | 6.5536  | 4.096   | Real | No  | Bare-<br>Metal |

| 11 | ZCU216 MTS<br>2021.1                                       | ZCU216_MTS_2021.1_RevB.zip         | В | ZCU216 | 2021.1   | 2.4     | 2.4     | Real | Yes | Bare-<br>Metal |

| 12 | ZCU208 DMA<br>Capture 2020.2                               | Zcu208_4g_play_cap_2020p2_RevC.zip | с | ZCU208 | 2020.2   | 4.0     | 4.0     | Real | No  | Bare-<br>Metal |

| 13 | ZCU111 DMA<br>Play Capture<br>2020.1                       | zcu111_dma_2020.1_RevA.zip         | A | ZCU111 | 2020.1   | 1.47456 | 1.47456 | Real | No  | Bare-<br>Metal |

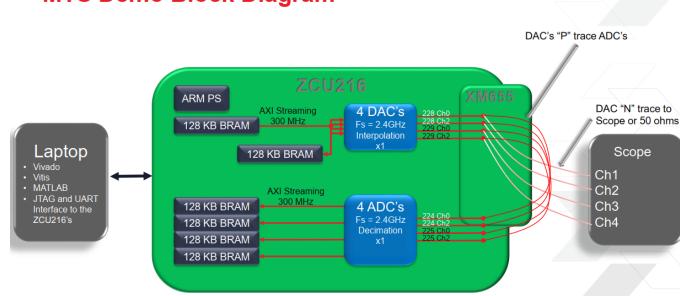

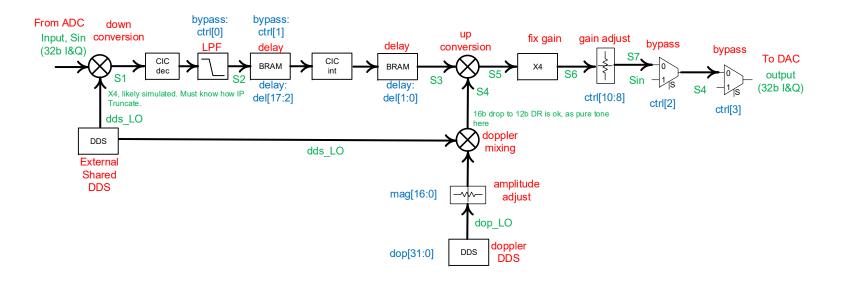

### Demonstration of design flow from RTL to Application C Code

- Use a reference design provided by Xilinx for ZCU216 RFSoC

Prototype Board

- Ref Design

- To show the code and result at various check points of design flow using Xilinx Vivado and Vitis

### MTS Demo Block Diagram

## **MATLAB DAC Tone Generator**

## Just gen wf and write to binary file, tcl cmd will sent this content to BRAM

New tones can be created using waveform\_gen\_bin\_export\_RevD.mlx The design comes with a pre-generated 100 MHz tone to use.

**Note**: This file slightly adjusts the frequency of the tone to properly fit into the number of samples. **Note:** All MATLAB and Octave files are in the folder .\Matlab folder. Choose that folder in MATLAB.

| 📣 MATLAB R2019a - sponsored third party support use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOME PLOTS APPS LIVE EDITOR INSERT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                             |

| New       Open       Save       Save | Contraction Run Contraction Run                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Live Editor - C:\rfsoc\ex_des\zcu216\mts\2p4g\v1\Matlab\waveform_gen_bin_export_RevD.mtx                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                             |

| Name ▲                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | waveform_gen_bin_export_RevD.mlx × +                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                             |

| waveform_cap_bin_import_MTS_MB_RevD.m<br>waveform_cap_bin_import_MTS_MB_RevD.mk<br>waveform_cap_bin_import_MTS_RevD.mk<br>waveform_cap_bin_import_RevD.mk<br>waveform_cap_bin_import_RevD.mk<br>waveform_gen_bin_export_RevD.mk<br>waveform_gen_bin_export_RevD.mk<br>waveform_gen_bin_export_RevD.mk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <pre>1 clc; % clear command line<br/>2 clear all; % clear all workspace variables<br/>3 close all; % close all plots<br/>4<br/>5 fs_converter = 2.40e9 % Sample rate in Hz<br/>6 frequency_requested = 100.0e6 % Target frequency for the tone.<br/>7 amplitude = -6; % desired output amplitude in dB<br/>8 interpolation_rate = 1; % Interpolation setting for the<br/>9 num_samples = 2^16; % The number of samples, 128k<br/>10 num_bits = 2^15 % The number of bits of resoluti</pre> | JFS<br>DAC                                                                                                                                                                                                                                                                                                                  |

| Note: All data files<br>are in the folder .\out<br>folder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <pre>11 amplitude_fs = 0; % amplitude in dBFS 12 13 filedir = '\out\' 14 %filedir = 'C:\rfsoc\ex_des\zcu111_dma_MIG_2019.2.1\out\' 15 filename = [filedir 'rfsoc_2p4e9_100m_1310725db.csv']; 16 filenamebin = [filedir 'rfsoc_2p4e9_100m_1310725db.bin']; 17 filenamebin2 = [filedir 'dac_output.bin']; 18 filenamebin3 = [filedir 'dac_output_dbfs.bin']; 10</pre>                                                                                                                        | <pre>% Relative directory for all data files<br/>% Or use full path name<br/>% Output CSV file, not used when running the design<br/>% Output bin file, not used when running the design<br/>% Output bin file, this is used when running the design<br/>% Output bin file for dBFS, not used when running the design</pre> |

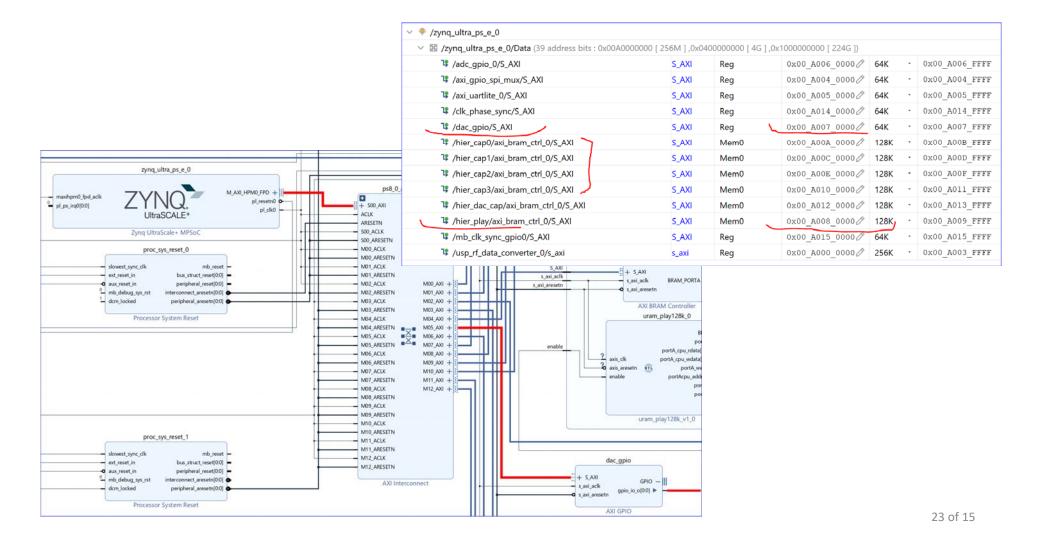

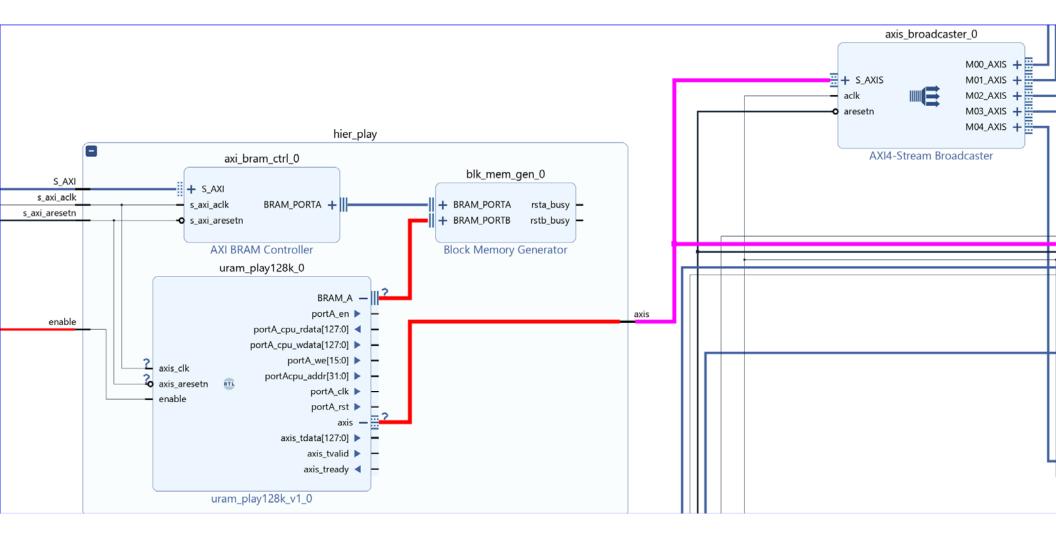

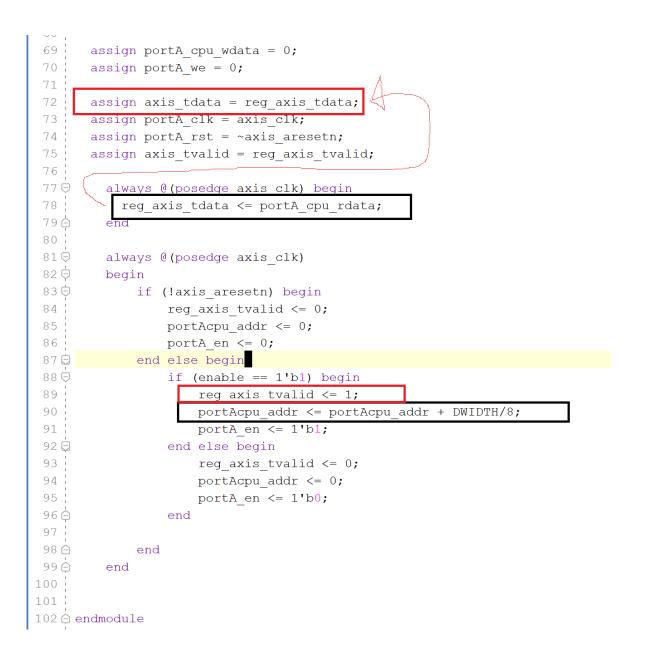

## **Download Waveform to memory**

Adr Editor: /hier\_play/axi\_bram\_ctrl\_0/S\_AXI is 0xa008000 of 128KB

#### download\_waveform.tcl performs the following functions.

- 1. Downloads the file 'dac\_output.bin' to 128kB of BRAM.

- 2. The file is downloaded to address 0xa0080000.

dow -force -data ./out/dac\_output.bin 0xa0080000

#targets -set 9; # 0x40001000

3. The default file is a 100 MHz tone in a 128 kB file size, 64k samples.

| Editor: /hier_play/axi_bram_ctrl_0/S_AXI is 0xa008000 of 128KB                                                                                                                        | <b>-</b>                                                                                                                                      | [ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---|

|                                                                                                                                                                                       | T XSCT Console 23                                                                                                                             | [ |

|                                                                                                                                                                                       | XSCT Process                                                                                                                                  |   |

| ownload_waveform.tcl performs                                                                                                                                                         | <pre>section, .heap: 0x0005ecc0 - 0x00060cbf section, .stack: 0x00060cc0 - 0x00063cbf</pre>                                                   |   |

| e following functions.                                                                                                                                                                | section, .coeff_mem: 0x000fdc00 - 0x000ffff                                                                                                   |   |

| Downloads the file                                                                                                                                                                    | 0% 0MB 0.0MB/s ??:?? ETA<br>26% 0MB 0.2MB/s ??:?? ETA                                                                                         |   |

| 'dac output.bin' to 128kB of                                                                                                                                                          | 56% 0MB 0.2MB/s ??:?? ETA<br>82% 0MB 0.2MB/s ??:?? ETA                                                                                        |   |

| BRAM.                                                                                                                                                                                 | 100% OMB 0.2MB/s 00:01                                                                                                                        |   |

| The file is downloaded to                                                                                                                                                             | Setting PC to Program Start Address 0x00000000<br>Successfully downloaded C:/rfsoc/ex des/zcu216/mts/2p4g/v1/ws/RFSOC CLI/Debug/RFSOC CLI.elf |   |

| address 0xa0080000.                                                                                                                                                                   | Info: Cortex-A53 #0 (target 10) Running                                                                                                       |   |

|                                                                                                                                                                                       | source download_waveform.tcl<br>Downloading player waveform                                                                                   |   |

| The default file is a 100 MHz                                                                                                                                                         | bownloading player wavelorm                                                                                                                   |   |

| tone in a 128 kB file <del>size, 6</del> 4k                                                                                                                                           | 0% 0MB 0.0MB/s ??:?? ETA                                                                                                                      |   |

|                                                                                                                                                                                       | 75% OMB 0.2MB/s ??:?? ETA<br>100% OMB 0.2MB/s 00:00                                                                                           |   |

| samples.                                                                                                                                                                              | Successfully downloaded C:/rfsoc/ex_des/zcu216/mts/2p4g/v1/out/dac_output.bin                                                                 |   |

|                                                                                                                                                                                       | xsct%                                                                                                                                         |   |

|                                                                                                                                                                                       |                                                                                                                                               |   |

|                                                                                                                                                                                       | xsctl                                                                                                                                         | _ |

| # Download player waveform to uram<br>puts "Downloading player waveform"<br>targets -set -filter {name =~ "PSU"};<br># targets -target-properties to find JTAG ID's - search for "lev | rel 0 name PSU"                                                                                                                               |   |

|                                                                                                                                                                                       |                                                                                                                                               |   |

source download\_waveform.tcl

| 59 //012345678901234567890123 01234567890123456789012345678901234567 |                                                 |

|----------------------------------------------------------------------|-------------------------------------------------|

| 60 {"####################################                            |                                                 |

| 61 #if URAM PLAY EN == 1                                             | j oj emocommerce jj                             |

| 62 \ {"dacMemPlay" \ , "- start the DAC URAM/BRAM player"            | , 0, *dacMemplay},                              |

| 63 {"dacMemStop", "- stop the DAC URAM/BRAM player"                  | , 0, *dacMemStop},                              |

| 64 // {"clkSync" , "- Sync Clock Modules" , 0, *cl                   |                                                 |

|                                                                      | .Koyne ;;                                       |

| 65                                                                   |                                                 |

|                                                                      |                                                 |

| 94 ************************************                              | **                                              |

| 95 #if URAM_PLAY_EN == 1                                             |                                                 |

| 96 <b>void dacMemPlay</b> (u32 *cmdVals)                             |                                                 |

| 97 {                                                                 |                                                 |

| 98 u32 tmpVal;                                                       | 19 #if URAM_PLAY_EN == 1                        |

| 99                                                                   | 20 #define GPIO_DAC_BASE XPAR_DAC_GPIO_BASEADDR |

| <pre>100 tmpVal = Xil_In32(GPIO_DAC_BASE);</pre>                     | 21                                              |

| 101 tmpVal = tmpVal   GPIO_DAC_PLAY_EN_MSK; //Set uram play enable   | 22 #define GPIO_DAC_PLAY_EN_MSK 0x1             |

| 102 Xil_Out32(GPIO_DAC_BASE, tmpVal);                                | 23 <b>#endif</b>                                |

| <pre>103 xil_printf("DAC BRAM player running. \n\r");</pre>          |                                                 |

| 104                                                                  |                                                 |

| 105 <b>return;</b>                                                   | 11CA (* DeCinitione Commentinhead) DAC CDTO */  |

|                                                                      | 1164 /* Definitions for peripheral DAC_GPIO */  |

| 106 }                                                                | 1165 #define XPAR DAC GPIO BASEADDR 0xA0070000  |

|                                                                      |                                                 |

000000000111111111222222222333333333

550 void cli\_uram\_play\_cap\_init(void) 56 **{** 57 static CMDSTRUCT cliCmds[] = {

> dacMemPlay DAC BRAM player running.

//00000000011111111112222

58

### □ Modify and/or insert own application

## Thank you