Course Title : Introduction to CMOS Analog Integrated Circuit Design

**Organising Group : ICDC**

Date : 27 Sept 2010

**Course Objective(s)**

: This course is aimed to introduce the participants to CMOS Analog IC Design. Building blocks circuits such as current mirror, voltage and current reference, differential amplifier and operational amplifier and their applications will be discussed. Electronic Design Automation tools will be use to simulate on some circuits in order to enhance the understanding of key parameters that determines the performance of the circuits.

| AM<br>Tan See Teck                                                                | PM<br>Teo Chee Keong                                                                                                                       |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Introduction</li> <li>CMOS Transistor</li> <li>CMOS Reference</li> </ul> | <ul> <li>Differential Amplifier</li> <li>Operational Amplifier</li> <li>Opamp Applications</li> <li>Opamp Design Considerations</li> </ul> |

| Lab1 & 2                                                                          | Lab 3                                                                                                                                      |

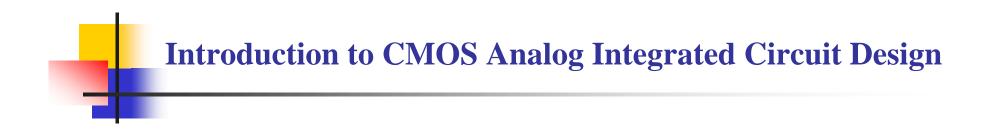

Difference between Analysis and Synthesis (design)

| Analysis                             | Design                                              |

|--------------------------------------|-----------------------------------------------------|

| Given a system, find its properties. | Given a set of properties or specifications, find a |

|                                      | system that meet the specifications.                |

| The solution is unique.              | No unique solution. Innovation in play.             |

| More like science.                   | More like art.                                      |

## Complexity of Analog Design:

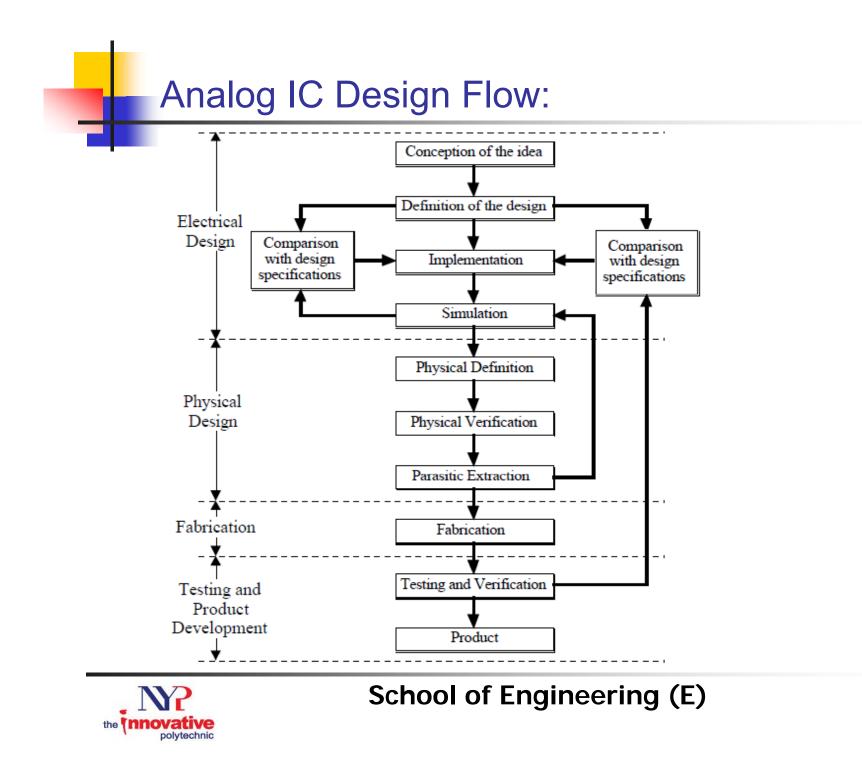

## Level of Hierarchy or Abstraction:

| Hierarchy               | Design                 | Physical                                            | Model            |

|-------------------------|------------------------|-----------------------------------------------------|------------------|

| System or architectural | System specifications  | Floor plan, pad<br>arrangement.                     | Behavioral model |

| Circuits                | Circuit specifications | Circuit Layout                                      | Macromodels      |

| Devices                 | Device specifications  | Geometrical<br>description, P-cell,<br>layout rules | Device models    |

Devices  $\rightarrow$  Handled by foundry. Process Design Kit (PDK) is the interface between foundry and circuit designer.

Systems  $\rightarrow$  Handled by system designer. Application or product level knowledge is required. Usually, system designer are also experienced circuit designer.

Circuits  $\rightarrow$  Domain of circuit designer.

#### System Level: Design

the novative polytechnic

## System Level: Design

System Design is top-down.

Get input from customer (through application/Product/Marketing engineer/manager).

Study datasheets of competitors.

Come out specifications of various circuits for circuit designer to work on.

System level simulation at SPICE level or behavior level.

- Complete versus partial system simulation?

- External component (model available?) to be included in the simulation?

#### System Level: Design

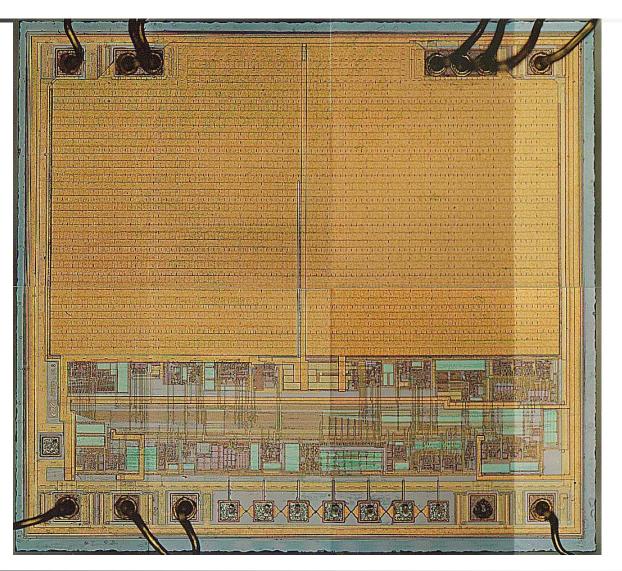

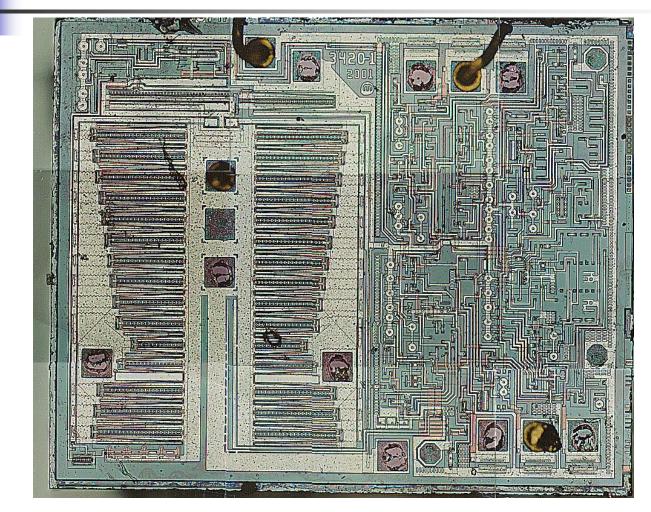

#### System Level: Layout

#### System Level: Layout

□ As long as it works, funny pad arrangement is acceptable.

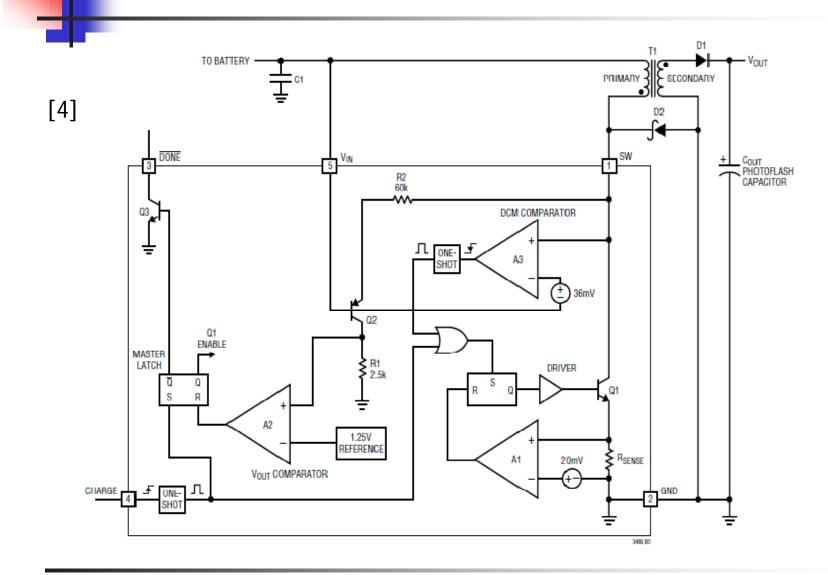

[4]

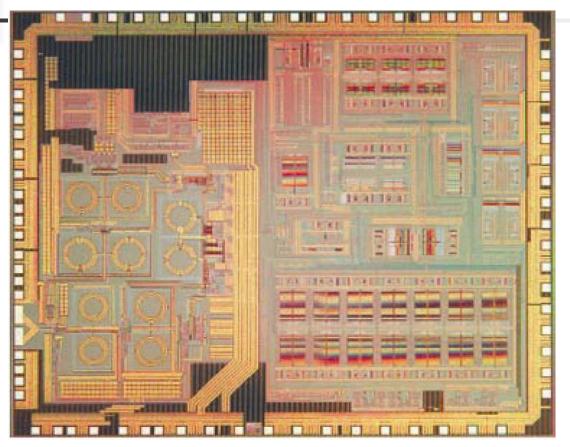

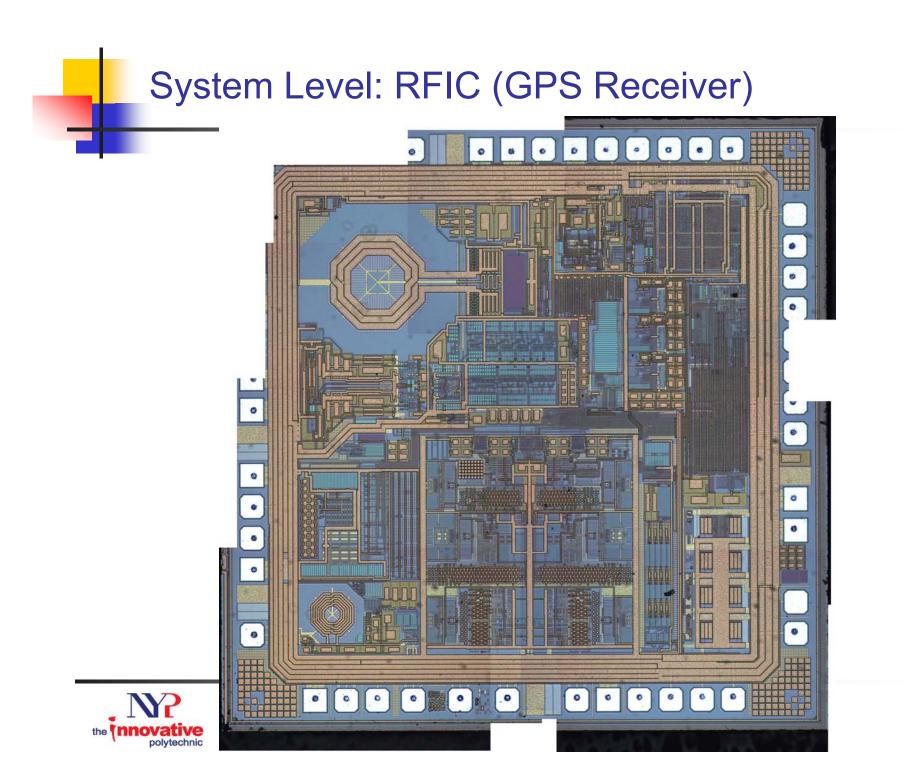

#### System Level: RFIC (Bluetooth Transceiver)

- L takes up area (cost).

- Meeting performance without using L?

- Burning more power against using L?

#### Process, Voltage and Temperature (PVT):

The system or circuits need to meet the specification under PVT variation.

• Process  $\rightarrow$  Various corner simulation to cater for process variation.

□ Voltage  $\rightarrow$  Example, 1.6 to 2.0V for 0.18um technology, 1.1 to 1.3V for 0.13um technology.

□ Temperature → Junction temperature. Depending on application. Such as -40°C to 120°C. What is the ambient temperature? What is the power dissipation and packaging adopted?

#### Process, Voltage and Temperature (PVT):

#### ABSOLUTE MAXIMUM RATINGS

| 4      | Vcc Pins to GND                            | 0.3V to +3.3V                     |

|--------|--------------------------------------------|-----------------------------------|

| Ň      | V <sub>CC</sub> Pins to Each Other         |                                   |

|        | FILT to GND                                | 0.3V to (V <sub>CC</sub> + 0.3V)  |

| X      | CMOS Inputs to GND (SHDN, SCLK,            |                                   |

| X      | CS, SDI)                                   | +0.3V to (V <sub>CC</sub> + 0.3V) |

|        | CMOS Outputs to GND (CLKOUT,               |                                   |

|        | GPSIF_, SDO)                               |                                   |

| Ś      | RFIN to GND                                |                                   |

| $\leq$ | First IF Filter I/O to GND (IFOUT±, IFIN±) | 0.3V to (V <sub>CC</sub> + 0.3V)  |

| Crystal Inputs to GND (XTAL, REFCLK)0.3V to (V <sub>CC</sub> + 0.3V) |

|----------------------------------------------------------------------|

| Maximum RF Input Power0dBm                                           |

| Continuous Power Dissipation (T <sub>A</sub> = +85°C)                |

| 28-Pin Thin QFN (derate 20.8mW/°C above +70°C) .1000mW               |

| Operating Temperature Range40°C to +85°C                             |

| Junction Temperature+150°C                                           |

| Storage Temperature Range65°C to +160°C                              |

| Lead Temperature (soldering, 10s)+300°C                              |

#### LT3468/LT3468-1

#### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| V <sub>IN</sub> Voltage<br>SW Voltage<br>CHARGE Voltage<br>DONE Voltage<br>Current into DONE Pin<br>Maximum Junction Temperature<br>Operating Temperature Range (Note 2)<br>Storage Temperature Range | 0.4V to 50V<br>10V<br>10V<br>10V<br> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Storage Temperature Range (Note 2)<br>Lead Temperature (Soldering, 10 sec)                                                                                                                            | -65°C to 150°C                       |

|                                                                                                                                                                                                       |                                      |

Ambient temperature to junction temperature will depends on thermal impedance of packaging.

# Analog Design versus Digital Design:

$\ \ \, \square \ \, Digital: Speed \leftrightarrow Power \leftrightarrow Area$

□ Analog: Speed ↔ Power ↔ Area ↔ Precision ↔ Gain ↔ Noise ↔ Linearity etc.

Analog Designer need to grasp multiple concepts simultaneously.

Must be able to make appropriate simplifications and assumptions.

## Analog Design versus Digital Design:

| Analog Circuits                                                                     | Digital Circuits                                                |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Analog Circuits                                                                     | Digital Circuits                                                |

| Signals are continuous in amplitude<br>and can be continuous or discrete in<br>time | Signals are discontinuous in amplitude and time – binary states |

| Designed at circuit level                                                           | Designed at the systems level using HDLs                        |

| Customised methodology                                                              | Standard methodology                                            |

| CAD tools are difficult to apply                                                    | CAD tools have been extremely successful                        |

| Requires precision modelling                                                        | Timing models only                                              |

| Performance optimised                                                               | Programmable by software                                        |

| Irregular blocks                                                                    | Regular blocks                                                  |

| Difficult to route automatically                                                    | Easy to route automatically                                     |

| Dynamic range is limited by power supplies and noise (and linearity)                | Dynamic range unlimited                                         |

| IP not easily portable                                                              | Pervasive with IPs                                              |

## Analog Design Productivity: [6]

While digital designers have improved their design methodology and adopted automation, analog and mixed-signal designers by and large have not.

More re-spins (2, 3 or 4?) for design of complex analog chip as compare to complex digital chip.

The mismatch in schedule and risk between analog and digital portion of mixed-signal (or SoC) design makes it difficult to justify combining analog and digital on the same chip.

Due to low-level of productivity, difficult to assembled a team that is large enough to take on a project and complete it in timely manner.

## Reference:

- 1. CMOS Analog Circuit Design, Phillip E. Allen & Douglas R. Holberg, 2<sup>nd</sup> ed.

- 2. Analog Integrated Circuit Design, David A. Johns & Ken Martin, John Wiley & Sons, Inc.

- 3. Design of Analog CMOS integrated Circuits, Behzad Razavi, McGraw-Hill International Edition.

- 4. LT3468, Photoflash Capacitor Charger.

- 5. MAX2741, Integrated L1-Band GPS Receiver.

- 6. The Designer's Guide To Verilog-AMS, Kenneth S. Kundert, 1<sup>st</sup> Ed.

- Digitally Assisted Pipeline ADCs, Theory and Implementation, Boris Murmann & Bernhard E. Boser

- 8. Analog Broadband Communication Circuits in Pure Digital Deep Sub-micron CMOS, Klaas Bult, ISSCC 1999

- 9. CMOS technology: Present and future, Bijan Davari, VLSI 1999

- 10. Motivation for RF Integration, Fujitus White Paper.